# Interfacing with ANT General Purpose Chipsets and Modules

# **Copyright Information and Usage Notice**

This information disclosed herein is the exclusive property of Dynastream Innovations Inc. No part of this publication may be reproduced or transmitted in any form or by any means including electronic storage, reproduction, execution or transmission without the prior written consent of Dynastream Innovations Inc. The recipient of this document by its retention and use agrees to respect the copyright of the information contained herein.

The information contained in this document is subject to change without notice and should not be construed as a commitment by Dynastream Innovations Inc. unless such commitment is expressly given in a covering document.

The Dynastream Innovations Inc. ANT Products described by the information in this document are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Dynastream product could create a situation where personal injury or death may occur. If you use the Products for such unintended and unauthorized applications, you do so at your own risk and you shall indemnify and hold Dynastream and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Dynastream was negligent regarding the design or manufacture of the Product.

©2010 Dynastream Innovations Inc. All Rights Reserved.

# **TABLE OF CONTENTS**

|                                               | INIKO                                                                                         | DUCTION                                                                                                                                                                                                                                                                                                                                                                               | 4                          |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2                                             | ASYNO                                                                                         | CHRONOUS SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                                             | 5                          |

| 2.1                                           | DESC                                                                                          | RIPTION                                                                                                                                                                                                                                                                                                                                                                               | 5                          |

| 2.2                                           | Port                                                                                          | PARAMETERS                                                                                                                                                                                                                                                                                                                                                                            | 5                          |

|                                               | 2.2.1                                                                                         | Communication Configuration                                                                                                                                                                                                                                                                                                                                                           | 5                          |

|                                               | 2.2.2                                                                                         | Port Select (PORTSEL)                                                                                                                                                                                                                                                                                                                                                                 | 5                          |

|                                               | 2.2.3                                                                                         | Speed Select (BR1, BR2, BR3*)                                                                                                                                                                                                                                                                                                                                                         | 5                          |

| 2.3                                           | LINK                                                                                          | LAYER PROTOCOL                                                                                                                                                                                                                                                                                                                                                                        | 6                          |

|                                               | 2.3.1                                                                                         | Characteristics                                                                                                                                                                                                                                                                                                                                                                       | 6                          |

|                                               | 2.3.2                                                                                         | Message Structure                                                                                                                                                                                                                                                                                                                                                                     | 6                          |

|                                               | 2.3.3                                                                                         | Message Details                                                                                                                                                                                                                                                                                                                                                                       | 6                          |

|                                               | 2.3.4                                                                                         | Optional Zero Pad Bytes                                                                                                                                                                                                                                                                                                                                                               | 7                          |

| 2.4                                           | ANT                                                                                           | Messages                                                                                                                                                                                                                                                                                                                                                                              | 7                          |

| 2.5                                           | RESE                                                                                          | T AND INITIALIZATION                                                                                                                                                                                                                                                                                                                                                                  | 7                          |

|                                               | 2.5.1                                                                                         | Resetting with the Software Reset                                                                                                                                                                                                                                                                                                                                                     | 7                          |

|                                               | 2.5.2                                                                                         | Resetting with the Reset Pin                                                                                                                                                                                                                                                                                                                                                          | 7                          |

|                                               | 2.5.3                                                                                         | Resetting via the DEEP SLEEP / SUSPEND Cycle                                                                                                                                                                                                                                                                                                                                          | 7                          |

| 2.6                                           | ASYN                                                                                          | CHRONOUS PORT CONTROL (RTS)                                                                                                                                                                                                                                                                                                                                                           | 8                          |

| 2.7                                           | Powe                                                                                          | R CONSERVATION                                                                                                                                                                                                                                                                                                                                                                        | 9                          |

|                                               | 2.7.1                                                                                         | Sleep Enable (SLEEP)                                                                                                                                                                                                                                                                                                                                                                  | 9                          |

|                                               |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                       |                            |

|                                               | 2.7.2                                                                                         | Suspend mode control ( SUSPEND )                                                                                                                                                                                                                                                                                                                                                      | 10                         |

| 3                                             |                                                                                               | Suspend mode control ( <u>SUSPEND</u> )                                                                                                                                                                                                                                                                                                                                               |                            |

| <b>3</b> .1                                   | SYNCH                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                       | 11                         |

|                                               | SYNCH                                                                                         | IRONOUS SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                                              | <b> 11</b><br>11           |

| 3.1                                           | SYNCH                                                                                         | IRONOUS SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                                              | <b> 11</b><br>11           |

| 3.1                                           | SYNCH<br>DESC<br>PORT                                                                         | IRONOUS SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                                              | 11<br>11<br>11             |

| 3.1                                           | DESC<br>PORT<br>3.2.1<br>3.2.2                                                                | RIPTION PARAMETERS  Port Select (PORTSEL)                                                                                                                                                                                                                                                                                                                                             | 11<br>11<br>11<br>11       |

| 3.1<br>3.2                                    | DESC<br>PORT<br>3.2.1<br>3.2.2                                                                | PARAMETERS                                                                                                                                                                                                                                                                                                                                                                            | 11 11 11 11 11             |

| 3.1<br>3.2                                    | SYNCH<br>DESC<br>PORT<br>3.2.1<br>3.2.2<br>LINK                                               | PARAMETERS                                                                                                                                                                                                                                                                                                                                                                            | 11<br>11<br>11<br>11<br>12 |

| 3.1<br>3.2                                    | SYNCH  DESC  PORT  3.2.1  3.2.2  LINK  3.3.1                                                  | HRONOUS SERIAL INTERFACE  RIPTION  PARAMETERS  Port Select (PORTSEL)  Flow Control Select (SFLOW)  LAYER PROTOCOL  Characteristics                                                                                                                                                                                                                                                    | 111111111212               |

| 3.1<br>3.2                                    | SYNCH  DESC  PORT  3.2.1  3.2.2  LINK  3.3.1  3.3.2  3.3.3                                    | IRONOUS SERIAL INTERFACE  RIPTION  PARAMETERS  Port Select (PORTSEL)  Flow Control Select (SFLOW)  LAYER PROTOCOL  Characteristics  Message Structure                                                                                                                                                                                                                                 | 11111111121212             |

| 3.1<br>3.2<br>3.3                             | SYNCH  DESC  PORT  3.2.1  3.2.2  LINK  3.3.1  3.3.2  3.3.3                                    | RIPTION PARAMETERS Port Select (PORTSEL) Flow Control Select (SFLOW)  LAYER PROTOCOL Characteristics Message Structure Message Details                                                                                                                                                                                                                                                | 11111112121212             |

| 3.1<br>3.2<br>3.3                             | SYNCH DESC PORT 3.2.1 3.2.2 LINK 3.3.1 3.3.2 3.3.3 SYNC                                       | RIPTION PARAMETERS Port Select (PORTSEL) Flow Control Select (SFLOW)  LAYER PROTOCOL Characteristics Message Structure Message Details HRONIZATION AND RESET                                                                                                                                                                                                                          | 11111112121213             |

| 3.1<br>3.2<br>3.3                             | SYNCH DESC PORT 3.2.1 3.2.2 LINK 3.3.1 3.3.2 3.3.3 SYNC 3.4.1                                 | RIPTION PARAMETERS Port Select (PORTSEL) Flow Control Select (SFLOW)  LAYER PROTOCOL Characteristics Message Structure Message Details HRONIZATION AND RESET Resetting with the Reset Pin                                                                                                                                                                                             | 111111121212121212         |

| 3.1<br>3.2<br>3.3                             | SYNCH DESC PORT 3.2.1 3.2.2 LINK 3.3.1 3.3.2 3.3.3 SYNC 3.4.1 3.4.2 3.4.3                     | RIPTION PARAMETERS Port Select (PORTSEL) Flow Control Select (SFLOW)  LAYER PROTOCOL Characteristics Message Structure Message Details HRONIZATION AND RESET Resetting with the Reset Pin Resetting with Synchronous Reset Sequence                                                                                                                                                   | 1111111212131414           |

| 3.1<br>3.2<br>3.3                             | SYNCH DESC PORT 3.2.1 3.2.2 LINK 3.3.1 3.3.2 3.3.3 SYNC 3.4.1 3.4.2 3.4.3 OPER                | RIPTION PARAMETERS Port Select (PORTSEL) Flow Control Select (SFLOW)  LAYER PROTOCOL Characteristics Message Structure Message Details HRONIZATION AND RESET Resetting with the Reset Pin. Resetting with Synchronous Reset Sequence. Resetting with the Software Reset                                                                                                               | 1111111212131414           |

| 3.1<br>3.2<br>3.3<br>3.4                      | SYNCH DESC PORT 3.2.1 3.2.2 LINK 3.3.1 3.3.2 3.3.3 SYNC 3.4.1 3.4.2 3.4.3 OPER SYNC           | IRONOUS SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                                              | 111112121313141414         |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6        | SYNCH DESC PORT 3.2.1 3.2.2 LINK 3.3.1 3.3.2 3.3.3 SYNC 3.4.1 3.4.2 3.4.3 OPER SYNC SYNC      | IRONOUS SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                                              | 1111111212131414141418     |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | SYNCH DESC PORT 3.2.1 3.2.2 LINK 3.3.1 3.3.2 3.3.3 SYNC 3.4.1 3.4.2 3.4.3 OPER SYNC SYNC POWE | RIPTION PARAMETERS  Port Select (PORTSEL)  Flow Control Select (SFLOW)  LAYER PROTOCOL.  Characteristics  Message Structure  Message Details  HRONIZATION AND RESET  Resetting with the Reset Pin.  Resetting with Synchronous Reset Sequence.  Resetting with the Software Reset  ATING MECHANISM  HRONOUS MESSAGING WITH BYTE FLOW CONTROL  HRONOUS MESSAGING WITH BIT FLOW CONTROL | 11111112121213141414141618 |

## 1 Introduction

ANT™ is a practical wireless sensor network protocol running on 2.4 GHz ISM band. Designed for ultralow power, ease of use, efficiency and scalability, ANT easily handles peer-to-peer, star, tree and practical mesh topologies. ANT provides reliable data communications, flexible and adaptive network operation and cross-talk immunity. ANT's protocol stack is extremely compact, requiring minimal microcontroller resources and considerably reducing system costs.

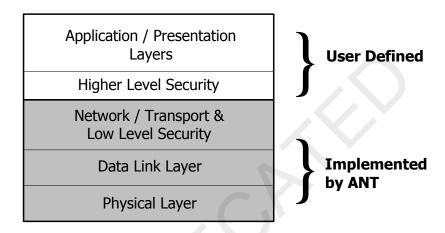

ANT provides carefree handling of the Physical, Network and Transport OSI layers. In addition, it incorporates key low-level security features that form the foundation for user-defined sophisticated network security implementations. ANT ensures adequate user control while considerably lightening computational burden in providing a simple yet effective wireless networking solution.

Figure 1-1. ISO Layers

The interface between ANT and the Host application has been designed with the utmost simplicity in mind such that ANT can be easily and quickly implemented into new devices and applications. The encapsulation of wireless protocol complexity within the ANT chipsets vastly reduces the burden on the application host controller, allowing a low-cost 4-bit or 8-bit microcontroller to establish and maintain complex wireless networks. Data transfers can be scheduled in a deterministic or ad-hoc fashion. A burst mode allows for the efficient transfer of large amounts of stored data to and from a PC or other computing device.

The intent of this document is to detail the interface requirements between an application microcontroller and the ANT products. It provides insight into both interface signals and physical layer data formats.

A complete description of the ANT Message protocol is found in the ANT Message Protocol and Usage document.

# 2 Asynchronous Serial Interface

## 2.1 Description

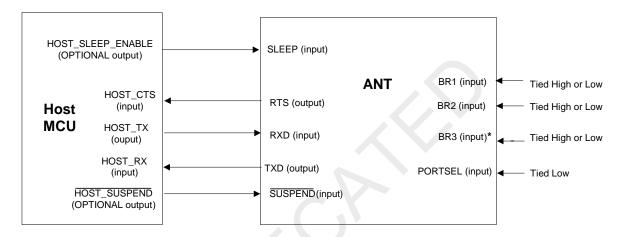

The Host MCU and ANT may communicate using the asynchronous mode of the serial interface. The connection diagram is shown below in Figure 2-1. Asynchronous mode is selected by tying the PORTSEL input low.

Refer to Section 3 for details on the alternative synchronous mode.

#### 2.2 Port Parameters

The asynchronous serial interface between ANT and the Host MCU is shown below in Figure 2-1.

\* Not available on all ANT devices

Figure 2-1. Asynchronous Mode Connections

## 2.2.1 Communication Configuration

Please note that all UART communication settings are for one start bit, one stop bit, 8 bits of data and no parity. Data is sent and received LSBit first.

## 2.2.2 Port Select (PORTSEL)

The PORTSEL signal should be tied low for asynchronous serial mode.

## 2.2.3 Speed Select (BR1, BR2, BR3\*)

The baud rate of the asynchronous communication between the Host and ANT is controlled by the speed select signals BR1, BR2 and BR3. Not all of these inputs are available on all ANT products. For more information, please refer to the datasheets of products of interest.

The table below shows the relationship between the states of the speed select signals and the corresponding baud rates.

| BR3* | BR2 | BR1 | <b>Baud Rate</b> |

|------|-----|-----|------------------|

| 0    | 0   | 0   | 4800             |

| 0    | 1   | 0   | 19200            |

| 0    | 0   | 1   | 38400            |

| 0    | 1   | 1   | 50000            |

| 1    | 0   | 0   | 1200*            |

| 1    | 1   | 0   | 2400*            |

| 1    | 0   | 1   | 9600             |

| 1    | 1   | 1   | 57600            |

<sup>\*</sup> Not available on all ANT devices. Refer to datasheets for capabilities. It is assumed to be of value 0 when not available.

Note that baud rate may have a significant impact on system current consumption. Refer to the Electrical Specifications section of the ANT product of interest for current consumption figures.

# 2.3 Link Layer Protocol

#### 2.3.1 Characteristics

The ANT interface protocol has the following characteristics:

- Binary protocol

- · Packets of variable length

- Each packet contains an 8-bit Checksum

- Asynchronous data is transmitted with 1 start, 8 data, 1 stop bit(s) and no parity, with standard CMOS level signaling

- Full duplex serial port

## 2.3.2 Message Structure

ANT and the Host MCU communicate by transmitting messages to each other. Each message is formatted as shown below.

| SYNC LENGTH ID DATA_1 DATA_2 DATA | TA_N CHECKSUM Opt. Opt. Zero Pad1 Pad2 |  |

|-----------------------------------|----------------------------------------|--|

|-----------------------------------|----------------------------------------|--|

Each variable-length message is sent starting with the SYNC byte and ending with the CHECKSUM. Bytes are sent LSBit first.

## 2.3.3 Message Details

| Byte #   | Bit # | Name                       | Length     | Description                                                                                 |

|----------|-------|----------------------------|------------|---------------------------------------------------------------------------------------------|

| 0        | 7:0   | SYNC                       | 1 Byte     | Fixed SYNC field = 10100100 (MSB:LSB)                                                       |

| 1        | -     | LENGTH                     | 1 Byte     | Number of data byes in the message                                                          |

| 2        | -     | ID                         | 1 Byte     | Data type identifier<br>0 : Invalid<br>1255 : Valid data type ID                            |

| 3N+2     | -     | DATA_1 DATA_N              | N Bytes    | Message data bytes                                                                          |

| N+3      | -     | CHECKSUM                   | 1 Byte     | XOR of all previous bytes (including SYNC)                                                  |

| N+4, N+5 | -     | Optional Zero PAD<br>Bytes | 1or2 Bytes | Zero PAD bytes may be required in conjunction with flow control when doing BURST transfers. |

The following is an example of how to encode/decode an ANT serial message.

ANT\_OpenChannel(1) -> SerialData (0xA4, 0x01, 0x4B, 0x01, 0xEF)

The details of the contents of this example serial message are shown in the table below.

| Byte # | Name     | Length | Data | Description                                                                                  |

|--------|----------|--------|------|----------------------------------------------------------------------------------------------|

| 0      | SYNC     | 1 Byte | 0xA4 | SYNC is always 0xA4                                                                          |

| 1      | LENGTH   | 1 Byte | 0x01 | Number of Data bytes in this message = 1                                                     |

| 2      | ID       | 1 Byte | 0x4B | ANT_OpenChannel message ID is 0x4B                                                           |

| 3      | DATA_1   | 1 Byte | 0x01 | There is 1 Data Byte in this message: This byte is Channel #. It has been set to Channel = 1 |

| 4      | CHECKSUM | 1 Byte | 0xEF | 0xA4 xor 0x01 xor 0x4B xor 0x01 = 0xEF                                                       |

#### 2.3.4 Optional Zero Pad Bytes

The RTS signal (described below) is raised by ANT after the last byte of a message has been received, therefore ANT will lose any further bytes that were sent, or in the process of being sent, by the host before the RTS signal is acted upon and transmission halted. To avoid this problem, either the messages need to be spaced apart by the Host MCU or 0-pad bytes need to be added to the end of each message being transmitted to handle whatever byte pipeline is in place. For example, when considering PC communication, two 0-bytes must be appended to every message, since PCs interpret CTS at the driver rather than the hardware level. ANT will discard 0-pad bytes received. This issue usually occurs only when using burst transfers from the Host to ANT and high data rates are expected.

## 2.4 ANT Messages

Refer to ANT Message Protocol and Usage document for details on the different types of messages and overall ANT protocol description.

#### 2.5 Reset and Initialization

For asynchronous communication, the ANT chipset is ready for communication after the initial power up phase has completed, as indicated by the RTS line. No further initialization is required.

There are several methods available to reset the ANT chip. For all reset methods, the configuration is cleared and goes back to default values, all channels are closed (and unassigned).

Resetting the ANT chipset or modules immediately following power-on conditions may be useful to ensure ANT is in a known state. If available, it is recommended that the  $\overline{\text{RESET}}$  pin be used to reset an ANT device on power up because it does not require the serial interface to be in the correct state.

## 2.5.1 Resetting with the Software Reset

The reset command  $(0x4A, ANT_ResetSystem)$  can be sent via the serial interface to reset the ANT chip. This is the most common method of resetting the chip.

## 2.5.2 Resetting with the Reset Pin

Some ANT devices provide an optional  $\overline{\text{RESET}}$  pin, intended for use when a system has a master reset source, or in the case of system failure. The major difference between the pin reset and the reset command is that the reset pin is slightly more thorough, resetting all I/O input states. The electrical characteristics of the  $\overline{\text{RESET}}$  signal are available in the datasheet of the specific ANT chipset or module. Please note that not all ANT chipsets/modules have a reset pin available.

## 2.5.3 Resetting via the DEEP SLEEP / SUSPEND Cycle

Coming out of the deep sleep or suspend mode will automatically trigger a reset of the ANT chip. In addition, if the SUSPEND signal is asserted directly from the ACTIVE state, ANT will reset and return to the ACTIVE state immediately. This method could be used to reset chips with no reset pin. This feature is available in asynchronous mode only.

## 2.6 Asynchronous Port Control (RTS)

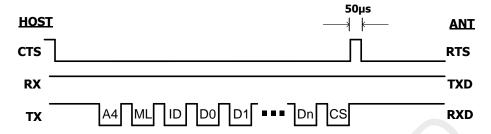

When ANT is configured in asynchronous mode, a full duplex asynchronous serial port is provided with flow control for data transmission from the Host to ANT. Flow control is performed by the RTS signal, which conforms to standard hardware flow control CMOS signal levels. The signal may therefore be attached to a PC serial port (with the use of an RS-232 level shifter), or to any other RS-232 device. The RTS signal is de-asserted for approximately 50  $_{\mu}s$  after each correctly formatted message has been received (Figure 2-2). This RTS signal duration is independent of the baud rate. Incorrect messages or partial messages are not acknowledged.

Figure 2-2. RTS Signal following a serial Host-> ANT transfer

When ANT raises the RTS signal high, the Host MCU may not send any more data until the RTS signal is lowered again. There is no flow control for data transmitted from ANT to Host, therefore the Host controller must be able to receive data at any time.

RTS is toggled following a reset on all ANT devices, except for nRF24AP1.

## 2.7 Power Conservation

## 2.7.1 Sleep Enable (SLEEP)

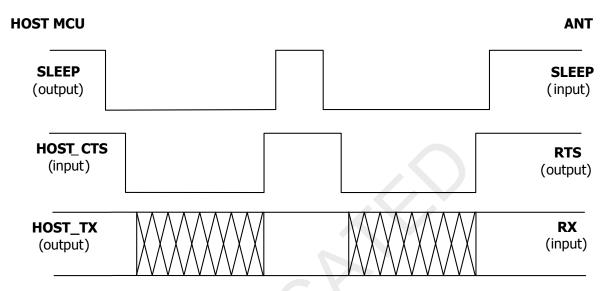

The SLEEP input signal allows ANT to sleep when the serial port is not required, helping conserve power. This control mechanism is illustrated below in Figure 2-3.

Figure 2-3. ANT Sleep control

If the SLEEP signal is not used, then it must be tied low. In this configuration, the ANT system will never sleep and will always be ready to receive data. The SUSPEND functionality cannot be used if the SLEEP signal is not used.

The SLEEP and RTS signals only affect the data being transferred from Host MCU to ANT. ANT will send data to the Host, when available, regardless of the state of these two signals.

**NOTE:** The RTS signal is raised by ANT after the last byte of a message has been received, therefore ANT will lose any further bytes that were sent, or in the process of being sent, by the host before the RTS signal is acted upon and transmission halted. To avoid this problem, either the messages need to be spaced apart by the Host MCU or 0-pad bytes need to be added to the end of each message being transmitted to handle whatever byte pipeline is in place. For example, when considering PC communication, two 0-bytes must be appended to every message, since PCs interpret CTS at the driver rather than the hardware level. ANT will discard 0-pad bytes received. This issue usually occurs only when using burst transfers from the Host to ANT and high data rates are expected.

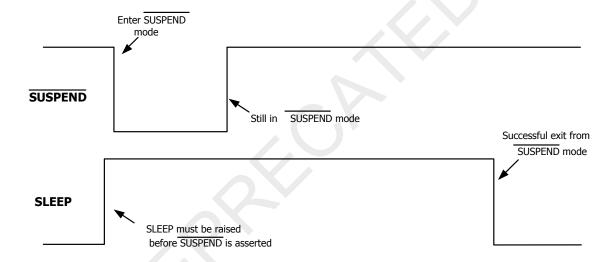

# 2.7.2 Suspend mode control ( SUSPEND )

Depending on the state of the SLEEP signal, asserting the SUSPEND signal will either:

- Cause ANT to terminate all RF and serial port activity and go into a defined low power state.

- Reset ANT device.

This will happen immediately, regardless of the state of the ANT system. This signal provides support for use in USB applications, where USB devices are required to quickly enter a low-power state through hardware control.

Entering and exiting from the SUSPEND mode requires the use of the SLEEP signal, in addition to the SUSPEND signal. The assertion of SUSPEND is only recognized if SLEEP is also asserted at the time. De-assertion of the SLEEP signal is the only method for exiting from SUSPEND mode, as shown in Figure 2-4. Following exit, all previous transactions and configurations will be lost – ANT will be in its power-up state.

Figure 2-4. SUSPEND signal usage

# 3 Synchronous Serial Interface

## 3.1 Description

This section details the synchronous serial interface between ANT and a Host MCU. This mode is selected by connecting the PORTSEL input high, and may be used with a hardware SPI port.

Please refer to Section 2 for details on the alternative asynchronous mode.

Note, when operating in synchronous mode careful attention to reset behavior is required to prevent inadvertent deadlock conditions between ANT and the Host MCU. Please see Section 3.4 for more details on this subject.

In synchronous mode, ANT uses a half-duplex synchronous master serial interface with message flow control. The Host must be configured as a synchronous slave. The interface is meant to accommodate either a hardware synchronous slave port or a simple I/O control on the Host MCU. Full flow control is maintained in both directions, therefore the Host MCU retains full control of the message flow and can halt incoming messages as required.

#### 3.2 Port Parameters

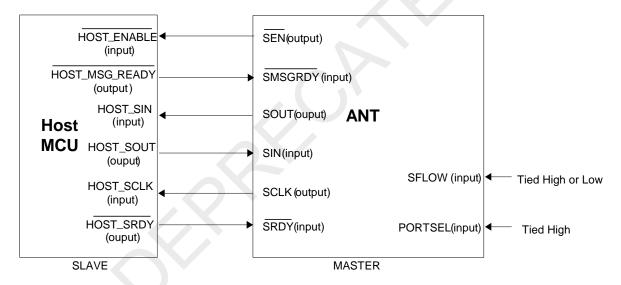

The synchronous serial interface between ANT and the Host MCU is shown below.

Figure 3-1. Synchronous Mode Connections

## 3.2.1 Port Select (PORTSEL)

The PORTSEL signal should be connected to logic high for synchronous serial mode.

## 3.2.2 Flow Control Select (SFLOW)

The Flow Control Select signal is used to configure the synchronous serial port for either Byte or Bit flow control.

| SFLOW | Flow Control      |

|-------|-------------------|

| 0     | Byte Flow Control |

| 1     | Bit Flow Control  |

Please note that Byte flow control assumes that the Host contains synchronous communication hardware which can be configured for synchronous slave communication. Bit flow control can be used when all serial lines are implemented in software on the Host MCU. The differences between byte and bit flow control are detailed in the sections below.

## 3.3 Link Layer Protocol

#### 3.3.1 Characteristics

The ANT interface protocol has the following characteristics:

- · Binary protocol

- Packets of variable length

- Each packet contains an 8-bit Checksum

- Data is transmitted LSB first

## 3.3.2 Message Structure

ANT and the Host MCU communicate by transmitting messages to each other. Each message is formatted as shown below.

| SYNC<br>R / W | MSG<br>LENGTH | MSG ID | DATA_1 | DATA_2 |  | DATA_N | CHECKSUM |

|---------------|---------------|--------|--------|--------|--|--------|----------|

|---------------|---------------|--------|--------|--------|--|--------|----------|

## 3.3.3 Message Details

| Byte # | Bit # | Description   | Length  | Description                                                           |

|--------|-------|---------------|---------|-----------------------------------------------------------------------|

| 0      | 7:1   | SYNC          | 7 bits  | Fixed SYNC field = 1010010 (MSB:LSB)                                  |

| 0      | 0     | R/W           | 1 bit   | 0 : Write (Message ANT → Host)<br>1 : Read (Message Host → ANT)       |

| 1      | -     | LENGTH        | 1 Byte  | Number of data byes in the message (Length should be between 1 and 9) |

| 2      |       | ID            | 1 Byte  | Data type identifier<br>0 : Invalid<br>1255 : Valid data type ID      |

| 3N+2   |       | DATA_1 DATA_N | N Bytes | Message data bytes<br>(There may be between 1 and 9 data bytes)       |

| N+3    | -     | CHECKSUM      | 1 Byte  | XOR of all previous bytes (including SYNC)                            |

The following is an example of how to encode a message to send from the Host to ANT.

ANT\_OpenChannel(1)

← SerialData (0xA5) // 0xA5 is read indicating that the Host may send a message to ANT

SerialData(0x01, 0x4B, 0x01, 0xEE) // The Host can then send the 4-byte message to ANT

| Byte # | Name     | Length | Direction | Data | Description                                                                                  |

|--------|----------|--------|-----------|------|----------------------------------------------------------------------------------------------|

| 0      | SYNC     | 1 Byte | ANT->Host | 0xA5 | SYNC is 0xA5 for a Host->ANT transaction                                                     |

| 1      | LENGTH   | 1 Byte | Host->ANT | 0x01 | Number of data bytes in this message = 1                                                     |

| 2      | ID       | 1 Byte | Host->ANT | 0x4B | ANT_OpenChannel message ID is 0x4B                                                           |

| 3      | DATA_1   | 1 Byte | Host->ANT | 0x01 | There is 1 Data Byte in this message: This byte is Channel #. It has been set to Channel = 1 |

| 4      | CHECKSUM | 1 Byte | Host->ANT | 0xFF | 0xA5 xor 0x01 xor 0x4B xor 0x01 = 0xFF                                                       |

The following is an example of how the Host would decode a message received from ANT.

- ← SerialData (0xA4, 0x02, 0x52, 0x01, 0x03, 0xF6) // The Host receives 6-byte message

- ← Channel\_Status(1, 3) // Decodes into a channel status message

| Byte # | Name     | Length | Direction | Data | Description                                                                   |

|--------|----------|--------|-----------|------|-------------------------------------------------------------------------------|

| 0      | SYNC     | 1 Byte | ANT->Host | 0xA4 | SYNC is 0xA4 for an ANT->Host transaction                                     |

| 1      | LENGTH   | 1 Byte | ANT->Host | 0x02 | Number of data bytes in this message = 2                                      |

| 2      | ID       | 1 Byte | ANT->Host | 0x52 | Channel_Status Message is 0x52                                                |

| 3      | DATA_1   | 1 Byte | ANT->Host | 0x01 | There are 2 data bytes in this message: This byte is Channel #. Channel = 1   |

| 4      | DATA_2   | 1 Byte | ANT->Host | 0x03 | This byte is the status. Status = 3, which indicates the channel is tracking. |

| 5      | CHECKSUM | 1 Byte | ANT->Host | 0xF6 | 0xA4 xor 0x02 xor 0x52 xor 0x01 xor 0x03 = 0xF6                               |

# 3.4 Synchronization and Reset

In order for the Host MCU to guarantee synchronization with ANT following a power up condition, it must reset ANT immediately after power-up or after any condition that results in loss of synchronization. The reset method depends on the specific ANT chipset or module being used, and the availability of a reset pin.

There are several methods available to reset the ANT chip. For all reset methods, the configuration is cleared and goes back to default values, all channels are closed (and unassigned). In synchronous mode the power state transitions are built into the serial protocol, therefore the SLEEP and SUSPEND reset options are not available.

## 3.4.1 Resetting with the Reset Pin

If available, asserting the  $\overline{\text{RESET}}$  signal on an ANT chip or module is the preferred reset method. A reset via this pin will have the same effect as a synchronization sequence. The electrical characteristics of the reset pin are detailed in the datasheet of the specific ANT chipset or module. Please note that not all ANT chips or modules have a reset pin available. If a reset pin is not available, then the Host MCU must apply a synchronous reset as detailed in the section below. While the reset pin is a simpler and quicker way of resetting an ANT part, care should be taken to ensure product will be compatible with all chips or chipsets that may be designed in.

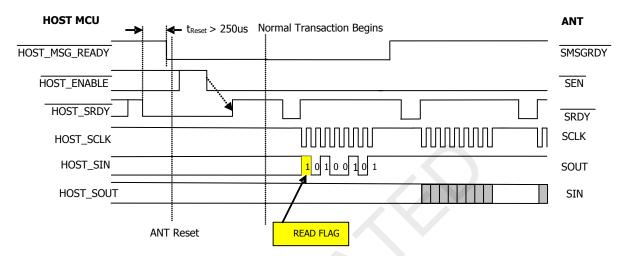

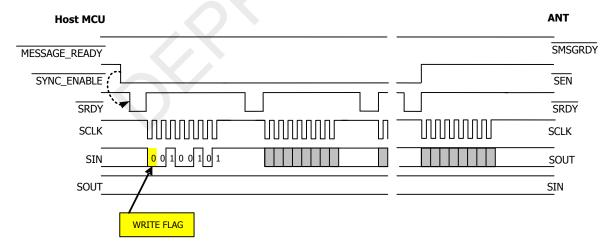

## 3.4.2 Resetting with Synchronous Reset Sequence

For ANT chips and modules that do not have a reset pin, a specific sequence known as the synchronous reset may be applied to ANT (Figure 3-2) instead. This synchronous reset is applicable to synchronous mode communication only, however it is supported by all ANT chipsets and modules (including those that support a reset pin).

Figure 3-2. Synchronization with ANT upon start-up

## 3.4.3 Resetting with the Software Reset

Once communication is established, the reset command (0x4A, ANT\_ResetSystem) can be sent via the serial interface to reset the ANT chip. The synchronization sequence does not need to be reapplied after the software reset. The major difference between the pin reset and the software reset is that the reset pin is slightly more thorough, resetting all I/O input states. Software reset is also only valid after communication is synchronized, and is not applicable in a power up state.

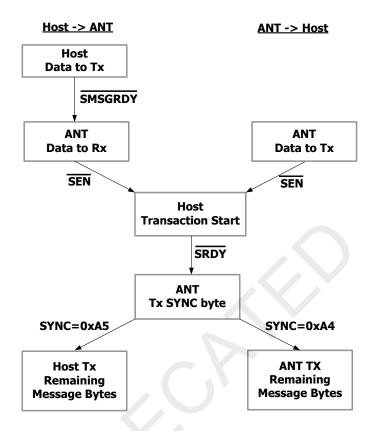

## 3.5 Operating Mechanism

A basic description of the communications mechanism follows.

- The synchronous serial port provided by ANT is a half duplex synchronous master, with full flow control in both directions of communication.

- Flow control of data transmitted to the Host MCU is controlled by the SRDY signal, and flow control of data transmitted to ANT is controlled by the master SCLK signal.

- By default, the Host is in receive mode and ANT is in transmit mode. In this state, ANT will forward all incoming radio messages to the Host as they become available. ANT uses the SEN signal to indicate the start of a message transaction and the Host will use the SRDY flow control to signal its readiness for incoming messages.

• SRDY must be asserted for communication to begin.

Figure 3-3. Synchronous Serial Communication

- Figure 3-3 and the timing diagrams in Figure 3-4 through Figure 3-7 for the basic message transaction sequence:

- For a message from Host->ANT:

- 1. The Host will assert the SMSGRDY signal indicating it wishes to enter into transmit mode.

- In either receive or transmit mode:

- 2. ANT will assert  $\ensuremath{\mathsf{SEN}}$  to indicate the start of a message transfer

- 3. After SEN has been asserted, the Host will assert SRDY to indicate it is ready for communication

- 4. After SEN and SRDY are both asserted, ANT always transmits the first (i.e. SYNC) byte. This is output from SOUT, and clocked with SCLK (see Section on Electrical Specifications for details of clock frequency). The lsb of the SYNC byte indicates the direction of the remaining message bytes (0 : Message Receive, ANT → Host; 1: Message Transmit, Host → ANT)

- 5. If the SYNC byte indicates a message receive (ANT->Host), the additional message bytes will be transmitted the same way as the SYNC byte.

- 6. If the SYNC byte indicates a message transmit (Host->ANT), the Host must output its data to ANT SIN at the clock rate provided by ANT SCLK.

- Data is transmitted least-significant-bit (Isb) first.

## 3.6 Synchronous Messaging with Byte Flow Control

Byte flow-control mode is used when a synchronous hardware serial port is available.

The Host MCU flow-control signal  $\overline{SRDY}$  can be implemented with a software controlled IO line or, in some cases, may be controlled by the Host's hardware serial port (e.g. EPSON MCU USART support for  $\overline{SRDY}$ ).

Data bits change state on the falling edge of SCLK and are read on the rising edge of SCLK. This is true for transactions in either direction.

The first byte (i.e. SYNC byte) in the transaction sequence is always sent from ANT to the Host MCU. The first bit of the SYNC byte dictates the direction for the remaining bytes in the transaction.

Shown below in Figure 3-4 to Figure 3-7 are examples of transactions between the Host and ANT in byte synchronous mode, using hardware or software  $\overline{SRDY}$  respectively.

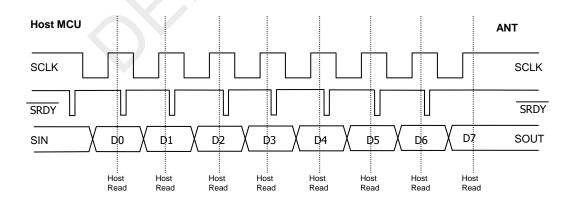

Figure 3-4. ANT -> Host Transaction (Hardware SRDY)

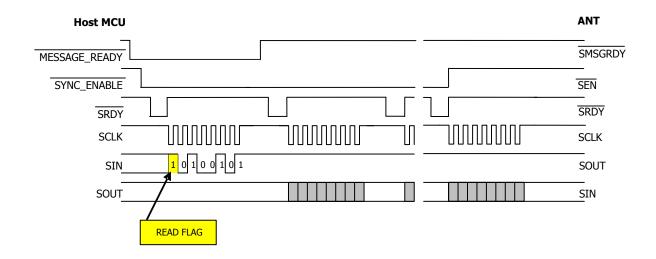

For ANT to host transactions with hardware SRDY (Figure 3-4), ANT asserts SEN and waits for the host to assert SRDY. Once both SEN and SRDY have been asserted, ANT will the send the SYNC byte from SOUT. For hardware SRDY, this signal will be de-asserted on the first SCLK transition. The first bit of the SYNC byte will notify the host of the message direction (i.e. ANT -> host), and the host will once again assert SRDY to receive the next message byte from ANT. Again, the hardware SRDY will deassert on the first SCLK transition and re-assert after each byte until the entire message has been transferred. After the last message byte, SRDY will remain de-asserted until the next message transaction is requested.

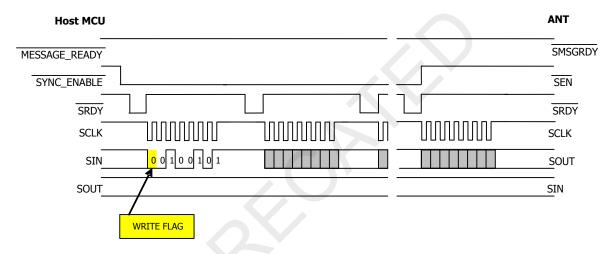

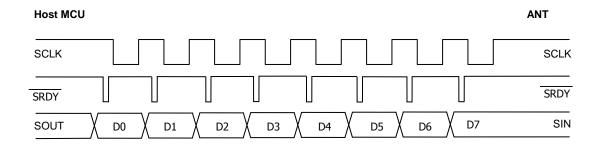

Figure 3-5. Host -> ANT Transaction (Hardware SRDY)

For host to ANT transactions with hardware SRDY (Figure 3-5), the process is very similar. The main difference is that the host first asserts SMSGRDY to inform ANT that it wished to send a message. ANT will respond by asserting SEN and then waiting for the host to assert SRDY. Once both SEN and have been asserted, ANT will the send the SYNC byte. For hardware SRDY, this signal will be deasserted on the first SCLK transition. The first bit of the SYNC byte will notify the host of the message direction (i.e. host->), and the host will once again assert SRDY and then send the next message byte to ANT on host SOUT at the rate of SCLK. Again, the hardware SRDY will de-assert on the first SCLK transition and re-assert after each byte until the entire message has been transferred. After the last message byte, SRDY will remain de-asserted until the next message transaction is requested.

Figure 3-6. ANT -> Host Transaction (Software SRDY)

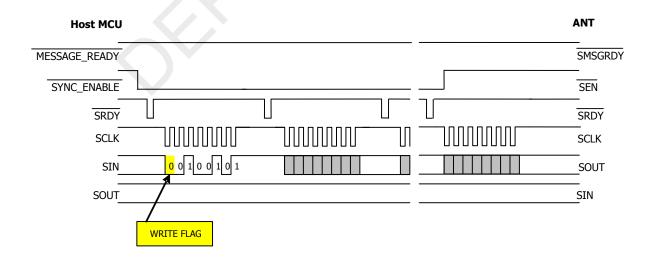

The process for ANT to host transactions with software SRDY (Figure 3-6) is very similar as for hardware SRDY. The sole difference is that the host can just pulse SRDY and does not have to wait until the first SCLK transition.

Figure 3-7. Host -> ANT Transaction (Software SRDY)

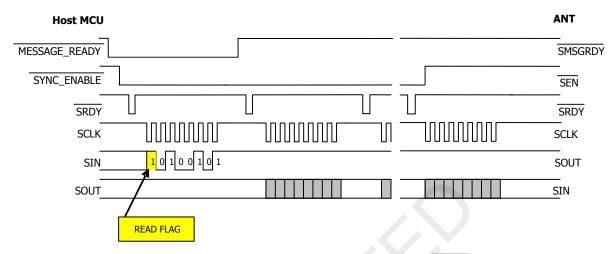

The process for host to ANT transactions with software SRDY (Figure 3-7) is very similar as for hardware SRDY. The only difference is that the host can pulse SRDY and does not have to wait until the first SCLK transition.

## 3.7 Synchronous Messaging with Bit Flow Control

If no SPI unit is available on the Host MCU, ANT can still be controlled using bit flow control. Using this method, the serial lines are implemented with software controlled IO lines. All of the signaling at the  $\frac{1}{1}$  message transaction level remains the same as above; however, instead of pulsing after every byte,  $\frac{1}{1}$  is pulsed for each bit of the message as shown below in .

Figure 3-8. ANT -> Host Byte Transaction (Software Bit Flow Control)

Figure 3-9. Host -> ANT Transaction (Software Bit Flow Control)

It is important to note that the Host MCU will do all bit processing on the rising edge of the SCLK signal, with the exception being when the byte is transmitted from Host MCU to ANT, and the first data bit will need to be asserted prior to the first clock edge. The final rising edge of the byte transaction will be the event to drive byte processing.

## 3.8 Power Up / Power Down

ANT will automatically place itself into deep sleep mode when all radio channels are closed and there is no activity on the  $\overline{SMSGRDY}$  input signal. The Host MCU should ensure these conditions during times that the ANT radio is not required in order to maximize product battery life.

Upon every power up, the host must apply the Synchronous Reset sequence as described in Section 3.4.

# 3.9 Serial Enable Control (ANT → Host)

The SEN signal, which is driven by ANT, will be asserted prior to message transmission. It can therefore be used as a serial port enable signal, which is useful in cases where the Host serial port requires hardware activation (Figure 3-10). The  $\overline{\text{SEN}}$  signal will be de-asserted by ANT on the first SCLK pulse of the last message byte.

Figure 3-10. Serial Enable Control using ANT

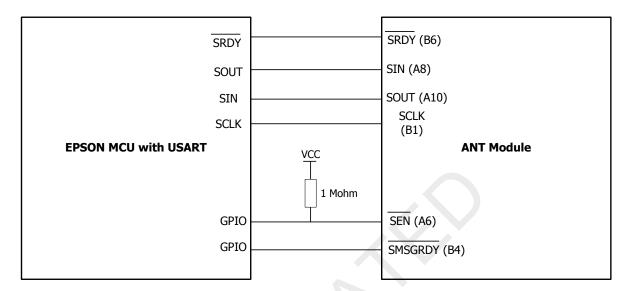

# 3.10 Using an Epson MCU as a Host controller

The interface has been designed to easily communicate with an EPSON microcontroller with a built-in USART. The EPSON should be configured in the following manner:

Figure 3-11. Example EPSON configuration for Byte Synchronous serial interface

For proper implementation of the above setup:

- 1. The GPIO connected to SEN must be configured as input.

- 2. The GPIO connected to SMSGRDY must be configured as output.

- 3. The EPSON USART must be configured as a synchronous slave.

- **4.** Configure the SRDY pin to be controlled by the USART. Note that the register flag that causes the SRDY pin to go low while waiting for a new byte must not be cleared until the SEN signal is seen to go low from the ANT device. This is to avoid causing a synchronization condition as mentioned in Section 3.4 above.

With the above setup, the EPSON MCU hardware USART will control the signaling on the  $\overline{SRDY}$ , SIN, SOUT and SCLK pins while the firmware (on the MCU) will handle signals on GPIOs connected to  $\overline{SEN}$  and  $\overline{SMSGRDY}$ .