#### FEATURES

- 2.4GHz worldwide ISM band

- SensRcore<sup>™</sup> development platform

- Ultra low power operation

- Simple sync/async serial interface

- Broadcast, Acknowledged, or Burst data transmissions

- 8 byte data payload per message

- Minimum message rate per ANT channel 0.5Hz

- ANT channel combined message rate up to 180Hz

- Burst transfer rate up to 20Kbps (true data throughput)

- 1 Mbps RF data rate

- Up to 1/4/8 ANT channels

- 125 selectable RF channels

- Up to 3 public, managed and/or private networks

- 2.0V to 3.6V supply voltage range

- -40°C to +85°C operating temperature

- RoHS compliant

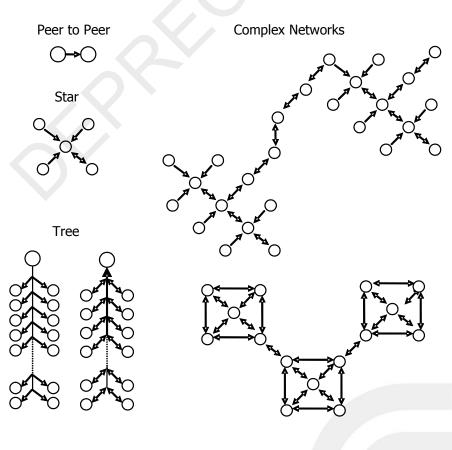

#### ANT NETWORK CONFIGURATIONS

#### **FAMILY MEMBERS**

ANT11TR13: 8 ANT channels ANT11TS53: 4 ANT channels; SensRcore™ ANT11TS63: 1 ANT channel; SensRcore™

D000001134 Rev 1.4

2 of 17

AT3 RF Transceiver Chipset, Rev 1.4

# **Table of Contents**

| TABL | E OF CO | NTENTS                        | 2  |

|------|---------|-------------------------------|----|

| NOTI | CES ANI | D RESTRICTED USE INFORMATION  | 3  |

| ANT  | OVERVI  | EW                            | 4  |

| 1    | АТЗ СН  | IIPSET                        | 5  |

| 1.1  |         | NT MCU                        |    |

|      | 1.1.1   | SensRcore™ Platform           | 5  |

|      | 1.1.2   | Pin-out                       | 5  |

|      | 1.1.3   | Asynchronous Baud Rate        | 7  |

|      | 1.1.4   | Crystal for clock system      | 7  |

| 1.2  | THE R   | ADIO CHIP                     | 8  |

| 2    | ELECTR  | RICAL SPECIFICATIONS          | 9  |

| 2.1  |         | ENT CALCULATION EXAMPLES      |    |

| 2.2  | A/D S   | PECIFICATIONS                 | 2  |

| 3    | SCHEM   | ATICS                         | 4  |

| 3.1  | ANT E   | BASEBAND PROCESSOR SCHEMATIC1 | 4  |

| 3.2  | INTER   | FACE EXAMPLES                 | 5  |

|      | 3.2.1   | Async Mode1                   | 5  |

|      | 3.2.2   | Byte Sync Mode                | 16 |

|      | 3.2.3   | Bit Sync Mode1                | 7  |

|      |         |                               |    |

AT3 RF Transceiver Chipset, Rev 1.4

3 of 17

# **Notices and Restricted Use Information**

#### **Restricted use of ANT RF Chipsets**

Operation of the RF chipsets in the development of future devices is deemed within the discretion of the user and the user shall have all responsibility for any compliance with any FCC regulation or other authority governing radio emission of such development or use. All products developed by the user must be approved by the FCC or other authority governing radio emission prior to marketing or sale of such products and user bears all responsibility for obtaining the authority's prior approval, or approval as needed from any other authority governing radio emission. Dynastream makes no representation with respect to the adequacy of the RF chipsets in developing low-power wireless data communications applications or systems. The RF Chipsets operate on shared radio channels. Any Products using ANT RF technology must be designed so that a loss of communications due to radio interference or otherwise will not endanger either people or property, and will not cause the loss of valuable data. Dynastream assumes no liability for the performance of products which are designed or created using the RF chipsets.

The Dynastream Innovations Inc. ANT Products described by the information in this following document are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Dynastream product could create a situation where personal injury or death may occur. If you use the Products for such unintended and unauthorized applications, you do so at your own risk and you shall indemnify and hold Dynastream and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Dynastream was negligent regarding the design or manufacture of the Product.

The information disclosed herein is the exclusive property of Dynastream Innovations Inc. and is not to be reproduced and/or distributed without the written consent of Dynastream Innovations Inc. No part of this publication may be reproduced or transmitted in any form or by any means including electronic storage, reproduction, execution or transmission without the prior written consent of Dynastream Innovations Inc. The recipient of this document by its retention and use agrees to respect the security status of the information contained herein.

The information contained in this document is subject to change without notice and should not be construed as a commitment by Dynastream Innovations Inc. unless such commitment is expressly given in a covering document

02009 Dynastream Innovations Inc. All Rights Reserved. ANT is a registered trade mark of Dynastream Innovations Inc.

4 of 17

AT3 RF Transceiver Chipset, Rev 1.4

## **ANT<sup>™</sup> Overview**

ANT<sup>™</sup> is a practical wireless sensor network protocol running on 2.4 GHz ISM band. Designed for ultra low power, ease of use, efficiency and scalability, ANT easily handles peer-to-peer, star, tree and practical mesh topologies. ANT provides reliable data communications, flexible and adaptive network operation and cross-talk immunity. ANT's protocol stack is extremely compact, requiring minimal microcontroller resources and considerably reducing system costs.

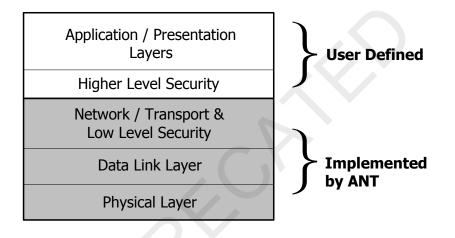

ANT provides carefree handling of the Physical, Network, and Transport OSI layers. In addition, it incorporates key low-level security features that form the foundation for user-defined, sophisticated, network-security implementations. ANT ensures adequate user control while considerably lightening computational burden in providing a simple yet effective wireless networking solution.

ANT supports public, managed and private network architectures with 2<sup>32</sup> uniquely addressable devices possible, ensuring that each device can be uniquely identified from each other in the same network.

ANT is proven with an installed base of over two million nodes in ultra low power sensor network applications in sport, fitness, home and industrial automation. The ANT solutions are available in chips, chipsets and modules to suit a wide variety of application needs.

A complete description of the ANT message protocol is found in the ANT Message Protocol and Usage document. The serial interface details are provided in the Interfacing with ANT General Purpose Chipsets and Modules document.

AT3 RF Transceiver Chipset, Rev 1.4

5 of 17

# 1 AT3 Chipset

AT3 (ANT11Txx3) chipsets are part of the General Purpose ANT Chipset family. Each chipset comprises an MSP430f2252, the ultra low power microcontroller (MCU) from Texas Instrument, and an nRF24L01 or nRF24L01+, the ultra low power radio chip from Nordic Semiconductor. SensRcore<sup>™</sup>, an easy-to-use design platform to build wireless sensors, is equipped in most of AT3 chipsets.

AT3 family of chipsets provides a comprehensive solution to the requirements of building a wireless sensor network consisting of nodes from simple sensors to complex hubs or control nodes. Common pin-outs enable easy network development, upgrade, migration and maintenance.

| AT3<br>Chipset | ANT MCU    | Pkg            | Radio Chip               | Pkg            | Description                                    |

|----------------|------------|----------------|--------------------------|----------------|------------------------------------------------|

| ANT11TR13      | ANTFTR2282 | QFN40<br>6x6mm | nRF24L01 or<br>nRF24L01+ | QFN20<br>4x4mm | 8 ANT channels                                 |

| ANT11TS53      | ANTFTS2242 | QFN40<br>6x6mm | nRF24L01 or<br>nRF24L01+ | QFN20<br>4x4mm | 4 ANT channels, SensRcore with 6 data channels |

| ANT11TS63      | ANTFTS2212 | QFN40<br>6x6mm | nRF24L01 or<br>nRF24L01+ | QFN20<br>4x4mm | 1 ANT channel, SensRcore with 4 data channels  |

AT3 chipset family has four standard parts:

### 1.1 The ANT MCU

The ANT MCU is an MSP430f2252 embedded with the ANT protocol. It provides the analog and digital inputs and outputs, serial interface to the Host MCU and SensRcore wireless sensor platform.

The serial interface to a host application can be either synchronous or asynchronous. Status and data messages are transferred bi-directionally to create and maintain communication channels, transmit data to and receive data from peripheral sensors and devices. Please refer to ANT Message Protocol and Usage document for details.

#### 1.1.1 SensRcore™ Platform

SensRcore is a wireless sensor development platform that is equipped with most AT3 chipsets. When using sensRcore to develop a wireless sensor, both analog and digital sensors can be directly connected to the ANT MCU. The normally required firmware development is replaced by writing a simple SensRcore script. An application host MCU could be eliminated from the system design. The result is a reduced component cost, size, power and the shortened development cycle of the target sensor device.

When AT3 chipsets are operated in sensRcore mode, the channel configuration parameters are stored in non-volatile memory and are enabled upon power-up. When I/O pins are configured as digital inputs or outputs, the electrical requirements are the same as all other signaling pins. When I/O pins are configured as analog inputs, different signal ranges can be selected with different reference voltages. The reference voltages available are  $V_{CC}$ , 2.5V, and 1.5V. Signals that exceed the specified reference level will be read by the A/D as a maximum value. Signal levels should not exceed  $V_{CC}$ . Each AIOx pin can be used as an analog input or a digital I/O pin; each IOx pin can be used only as a digital I/O pin. I/O pins that are not being used in a specific SensRcore mode configuration should be left configured as digital inputs, which is the default setting.

ANT sensRcore scripts consist of ANT messages and commands. Please refer to "ANT Message Protocol and Usage" and "SensRcore Messaging and Usage". The script can be generated by using the software tool *SensRware*. There are 200 bytes available in the non volatile memory for SensRcore script.

When developing products, it is recommended to properly leave the access to the ANT MCU serial interface so that SensRcore script can be loaded. Service is provided for volume SensRcore script programming.

#### 1.1.2 Pin-out

The pin-out table for the ANT MCU is specified below. Please refer to the MSP430f2252/4 datasheet for any specific pin requirements.

6 of 17

AT3 RF Transceiver Chipset, Rev 1.4

| Pin # | Pin Name              | Pin Function   | Description                                                                                                     |

|-------|-----------------------|----------------|-----------------------------------------------------------------------------------------------------------------|

| 1     | DV <sub>ss</sub>      |                | Digital ground reference                                                                                        |

| 2     | XOUT                  | Output         | 32.768kHz crystal output                                                                                        |

| 3     | XIN                   | Input          | 32.768kHz crystal input                                                                                         |

| 4     | DV <sub>ss</sub>      |                | Digital ground reference                                                                                        |

| 5     | RST                   | Input          | Active low reset pin                                                                                            |

| 6     | SUSPEND<br>/SRDY/AIO0 | Input          | Async -> Suspend control<br>Sync -> Serial port ready<br>SensRcore Mode -> Analog/Digital input output          |

| 7     | SLEEP/MRDY/AIO1       | Input          | Async -> Sleep mode enable<br>Sync -> Message ready indication<br>SensRcore Mode -> Analog/Digital input output |

| 8     | TIE_GND1              | Input          |                                                                                                                 |

| 9     | BR2 / SCLK / DevSel2  | Input / Output | Async -> Baud rate selection<br>Sync -> Clock output signal<br>SensRcore Mode -> Configuration selection        |

| 10    | RF_MOSI               | Output         | Data output                                                                                                     |

| 11    | RF_MISO               | Input          | Data input                                                                                                      |

| 12    | RF_SCK                | Input          | SPI clock                                                                                                       |

| 13    | AV <sub>ss</sub>      |                | Analog ground reference                                                                                         |

| 14    | AV <sub>CC</sub>      |                | Analog supply voltage                                                                                           |

| 15    | 105                   | Input          | SensRcore Mode -> Digital input output                                                                          |

| 16    | PORTSEL               | Input          | Asynchronous or Synchronous port select<br>SensRcore Mode -> Demo script or user scripts                        |

| 17    | 107                   | Input          | SensRcore Mode -> Digital input output                                                                          |

| 18    | TIE_GND2              | Input          |                                                                                                                 |

| 19    | LED                   | Output         |                                                                                                                 |

| 20    | TIE_GND3              | Input          |                                                                                                                 |

| 21    | TIE_GND5              | Input          |                                                                                                                 |

| 22    | TIE_GND4              | Input          |                                                                                                                 |

| 23    | TXD0/SOUT/IO6         | Output         | Async -> Transmit data signal<br>Sync -> Data output<br>SensRcore Mode -> Digital input output                  |

| 24    | RXD0/SIN/AIO2         | Input          | Async -> Receive data signal<br>Sync -> Data input<br>SensRcore Mode -> Analog/Digital output                   |

| 25    | BR1/SFLOW/DevSel1     | Input          | Async -> Baud rate selection<br>Sync -> Bit or Byte flow control select                                         |

| 26    | BR3/DevSel3           | Input          | Async -> Baud rate selection<br>Sync -> Configuration selection                                                 |

| 27    | AIO3/VRef-/VeRef      | Input/Output   | SensRcore Mode -> Analog/Digital output;<br>Negative reference voltage input/output                             |

AT3 RF Transceiver Chipset, Rev 1.4

7 of 17

| Pin # | Pin Name          | Pin Function | Description                                                                                 |

|-------|-------------------|--------------|---------------------------------------------------------------------------------------------|

| 28    | AIO4/VRef+/VeRef+ | Input/Output | SensRcore Mode ->Analog/Digital Output;<br>Positive reference voltage input/output          |

| 29    | RTS/SEN/IOSEL     | Output       | Async -> Request to send<br>Sync -> Serial enable signal<br>SensRcore Mode -> IOSEL tie low |

| 30    | TIE_GND6          | Input        |                                                                                             |

| 31    | RF_IRQ            | Input        | Maskable interrupt pin                                                                      |

| 32    | RF_CE             | Output       | Radio chip enable                                                                           |

| 33    | RF_CSN            | Output       | SPI chip select                                                                             |

| 34    | TIE_GND7          | Input        |                                                                                             |

| 35    | TIE_GND8          | Input        |                                                                                             |

| 36    | TIE_GND9          | Input        |                                                                                             |

| 37    | TIE_GND10         | Input        |                                                                                             |

| 38    | DV <sub>CC</sub>  |              | Digital supply voltage                                                                      |

| 39    | DV <sub>CC</sub>  |              | Digital supply voltage                                                                      |

| 40    | TIE_GND11         | Input        |                                                                                             |

### 1.1.3 Asynchronous Baud Rate

The baud rate of the asynchronous communication is controlled by the speed select signals BR1, BR2 and BR3. The table below shows the relationship between the states of the speed select signals and the corresponding baud rates.

| BR3 | BR2 | BR1 | Baud Rate |

|-----|-----|-----|-----------|

| 0   | 0   | 0   | 4800      |

| 0   | 1   | 0   | 19200     |

| 0   | 0   | 1   | 38400     |

| 0   | 1   | 1   | 50000     |

| 1   | 0   | 0   | 1200      |

| 1   | 1   | 0   | 2400      |

| 1   | 0   | 1   | 9600      |

| 1   | 1   | 1   | 57600     |

### 1.1.4 Crystal for clock system

ANT operation requires the 32.768kHz crystal for the MCU clock system meeting the following specification.

| Delta F Tolerance   | +/- 20ppm @25°C (+/-50ppm Max)                                       |

|---------------------|----------------------------------------------------------------------|

| CI Load Capacitance | 11pF (Includes Bond and package capacitance but not PCB capacitance) |

8 of 17

AT3 RF Transceiver Chipset, Rev 1.4

### 1.2 The Radio Chip

The radio chip of AT3 chipset is the nRF24L01 or nRF24L01+ transceiver chip from Nordic Semiconductor. The pin-out of the radio is listed in the Table below. Please refer to the nRF24L01 or nRF24L01+ datasheet for any specific pin requirements.

| Pin # | Pin Name            | Pin Function  | Description                             |

|-------|---------------------|---------------|-----------------------------------------|

| 1     | RF_CE               | Input         | Radio chip enable                       |

| 2     | RF_CSN              | Input         | SPI chip select                         |

| 3     | RF_SCK              | Input         | SPI clock                               |

| 4     | RF_MOSI             | Input         | SPI slave data input                    |

| 5     | RF_MISO             | Output        | SPI slave data output                   |

| 6     | RF_IRQ              | Output        | Maskable interrupt pin                  |

| 7     | V <sub>CC</sub>     | Power         | Power supply                            |

| 8     | V <sub>SS</sub>     | Power         | Ground                                  |

| 9     | XC2                 | Analog Output | Crystal pin2                            |

| 10    | XC1                 | Analog Input  | Crystal pin 1                           |

| 11    | V <sub>CC</sub> _PA | Power         | Power supply to power amplifier         |

| 12    | ANT1                | RF            | Antenna interface 1                     |

| 13    | ANT2                | RF            | Antenna interface 2                     |

| 14    | V <sub>SS</sub>     | Power         | Ground                                  |

| 15    | V <sub>cc</sub>     | Power         | Power supply                            |

| 16    | I <sub>REF</sub>    | Analog Input  | Reference current                       |

| 17    | V <sub>SS</sub>     | Power         | Ground                                  |

| 18    | Vcc                 | Power         | Power supply                            |

| 19    | DV <sub>CC</sub>    | Power Output  | Positive digital supply for de-coupling |

| 20    | V <sub>SS</sub>     | Power         | Ground                                  |

AT3 RF Transceiver Chipset, Rev 1.4

9 of 17

## 2 Electrical Specifications

NOTE: Please refer to the latest version of MSP430f2252/4 datasheet from Texas Instrument.

**NOTE:** Please refer to the latest version of the nRF24L01 or nRF24L01+ datasheet from Nordic Semiconductor.

| Absolute Maximum Rat                                  | ings                           |

|-------------------------------------------------------|--------------------------------|

| Voltage applied at $V_{\text{CC}}$ to $V_{\text{SS}}$ | -0.3V to +3.6V                 |

| Input voltage at any pin                              | -0.3V to $V_{\text{CC}}$ +0.3V |

| Diode current at any pin                              | ±2mA                           |

| Operating temperature                                 | -40°C to +85°C                 |

| Storage temperature                                   | -40°C to +105°C                |

**Note:** Stress exceeding one or more of the absolute maximum ratings may cause permanent damage to the chipsets.

Conditions:  $V_{CC}$  = +2.0V,  $V_{SS}$  = 0V,  $T_A$  = - 40°C to +85°C

| Symbol                   | Parameter (condition)                                                                                | Notes | Min                       | Тур | Max             | Units    |

|--------------------------|------------------------------------------------------------------------------------------------------|-------|---------------------------|-----|-----------------|----------|

|                          | Operating conditions                                                                                 |       |                           |     |                 |          |

| V <sub>CC</sub>          | Supply voltage                                                                                       |       | 2.2                       |     | 3.6             | V        |

| TEMP                     | Operating temperature                                                                                |       | -40                       |     | +85             | ٥C       |

|                          | Digital input pin                                                                                    |       |                           |     |                 |          |

| V <sub>IH</sub>          | HIGH level input voltage                                                                             |       | 1.9                       |     | $V_{CC}$        | V        |

| V <sub>IL</sub>          | LOW level input voltage                                                                              |       | $V_{SS}$                  |     |                 | V        |

|                          | Digital output pin                                                                                   |       |                           |     |                 |          |

| V <sub>OH</sub>          | HIGH level output voltage ( $I_{OH}$ =-0.5mA)                                                        |       | V <sub>cc</sub> -<br>0.25 |     | V <sub>cc</sub> | V        |

| V <sub>OL</sub>          | LOW level output voltage ( $I_{OL}$ =0.5mA)                                                          |       | $V_{SS}$                  |     | 0.25            | V        |

|                          | Analog input pin                                                                                     |       |                           |     |                 |          |

| V <sub>Analog</sub>      | Input voltage range                                                                                  | 4)    | $V_{SS}$                  |     | $V_{CC}$        | V        |

| F <sub>Sample</sub>      | Sample rate                                                                                          | 5)    | 0.002                     |     | 500             | Sample/s |

|                          | Counter input pin                                                                                    |       |                           |     |                 |          |

| F <sub>Counter</sub>     | Input frequency                                                                                      |       |                           |     | 1000            | Hz       |

|                          | Synchronous serial timing                                                                            |       |                           |     |                 |          |

| SCLK freq.               | Synchronous clock frequency (byte mode)                                                              |       | 285                       | 300 | 315             | kHz      |

| $t_{ReadValid}$          | Data is valid on read before low-to-high transition on the clock (byte mode)                         |       | 0.5                       |     |                 | μs       |

| $t_{WriteValid}$         | Data must be valid on write within this time after a high-to-low transition on the clock (byte mode) |       |                           |     | 2               | μs       |

| t <sub>SRDY_MinLow</sub> | Minimum SRDY low time                                                                                |       | 2.5                       |     |                 | μs       |

| t <sub>Reset</sub>       | Synchronous Reset. SRDY falling edge to MRDY falling edge                                            |       | 250                       |     |                 | μs       |

10 of 17

AT3 RF Transceiver Chipset, Rev 1.4

| Symbol                                         | Parameter (condition)                                                 | Notes | Min  | Тур  | Max  | Units |

|------------------------------------------------|-----------------------------------------------------------------------|-------|------|------|------|-------|

|                                                | General RF conditions                                                 |       |      |      |      |       |

| f <sub>OP</sub>                                | Operating frequency                                                   | 1)    | 2400 |      | 2524 | MHz   |

| F <sub>CHANNEL</sub>                           | Channel spacing                                                       |       |      | 1    |      | MHz   |

| $\Delta f$                                     | Frequency deviation                                                   |       |      | ±156 |      | kHz   |

|                                                | Current consumption                                                   |       |      |      |      |       |

| $\mathbf{I}_{Idle}$                            | No active channels – no communications                                |       |      | 1.1  |      | μA    |

| $I_{Suspend}$                                  | Asynchronous suspend activated                                        |       |      | 1.1  |      | μA    |

| $\mathbf{I}_{Base}$                            | Base active current                                                   |       |      | 2.6  |      | μA    |

| $\mathbf{I}_{sample}$                          | Average current/analog sample                                         |       |      | 0.5  |      | μA    |

| $I_{SC\ RF}$                                   | Average current/ ANT message in sensRcore mode                        |       |      | 13   |      | μA    |

| I <sub>Msq Rx ByteSync</sub>                   | Average current / Rx message in byte sync mode                        |       |      | 10.5 |      | μA    |

| I <sub>Msq Rx BitSync</sub>                    | Average current / Rx message in bit sync mode                         |       |      | 13.1 |      | μA    |

| I <sub>Msg_Rx_57600</sub>                      | Average current / Rx message in Async mode at 57600 baud              |       |      | 9.1  |      | μA    |

| I <sub>Msg_Rx_19200</sub>                      | Average current / Rx message in Async mode at 19200 baud              |       |      | 10.4 |      | μA    |

| $I_{\rm Msg_Rx\_4800}$                         | Average RF current / Rx message in Async mode at 4800 baud            |       |      | 8.5  |      | μA    |

|                                                |                                                                       |       |      |      |      |       |

| $I_{\text{Msg}_{\text{Tx}_{\text{ByteSync}}}}$ | Average current / Tx-only message in byte sync mode                   |       |      | 6.4  |      | μA    |

| I <sub>Msq Tx BitSync</sub>                    | Average current / Tx-only message in bit sync mode                    |       |      | 10.8 |      | μA    |

| I <sub>Msg_Tx_57600</sub>                      | Average current / Tx-only message in Async mode at 57600 baud         |       |      | 5.7  |      | μA    |

| I <sub>Msg_Tx_19200</sub>                      | Average current / Tx-only message in Async mode at 19200 baud         |       |      | 7.5  |      | μA    |

| $I_{Msg_Tx_{4800}}$                            | Average current / Tx-only message in Async mode at 4800 baud          |       |      | 4.4  |      | μA    |

|                                                |                                                                       |       |      |      |      |       |

| $I_{\text{Msg}_{\text{TR}}\text{ByteSync}}$    | Average current / Tx message in byte sync mode                        |       |      | 14.1 |      | μA    |

| $I_{Msq} ~ {}_{TR} ~ {}_{BitSync}$             | Average current / Tx message in bit sync mode                         |       |      | 18.4 |      | μA    |

| $I_{Msg_TR_57600}$                             | Average current / Tx message in Async mode at 57600 baud              |       |      | 13.5 |      | μA    |

| $I_{Msg_{TR}_{19200}}$                         | Average current / Tx message in Async mode at 19200 baud              |       |      | 15.0 |      | μA    |

| $\mathrm{I}_{\mathrm{Msg}}\mathrm{Tr}_{4800}$  | Average current / Tx message in Async mode at 4800 baud               |       |      | 11.7 |      | μA    |

| T                                              | Average current / Acknowledged message in byte                        |       |      | 19.6 |      |       |

| I <sub>Msg_Ack_ByteSync</sub>                  | sync mode<br>Average current / Acknowledged message in bit sync       |       |      |      |      | μA    |

| I <sub>Msg_Ack_BitSync</sub>                   | mode<br>Average current / Acknowledged message in Async               |       |      | 23.4 |      | μA    |

| I <sub>Msg_Ack_57600</sub>                     | mode at 57600 baud<br>Average current / Acknowledged message in Async |       |      | 18.7 |      | μA    |

| I <sub>Msg_Ack_19200</sub>                     | mode at 19200 baud                                                    |       |      | 19.9 |      | μA    |

| $I_{\rm Msg\_Ack\_4800}$                       | Average current / Acknowledged message in Async mode at 4800 baud     |       |      | 17.2 |      | μA    |

AT3 RF Transceiver Chipset, Rev 1.4

11 of 17

| Symbol              | Parameter (condition)                                  | Notes | Min | Тур  | Max  | Units |

|---------------------|--------------------------------------------------------|-------|-----|------|------|-------|

| $\mathbf{I}_{Peak}$ | Peak Current consumption                               |       |     | 19   |      | mA    |

| I <sub>PeakTx</sub> | Peak Current – Tx-only @ 0dBm                          |       |     | 13   |      | mA    |

| I <sub>Ave</sub>    | Broadcast Tx-only @ 0.5Hz in byte sync mode            |       |     | 5.8  |      | μA    |

| I <sub>Ave</sub>    | Broadcast Tx-only @ 2Hz in byte sync mode              |       |     | 15.4 |      | μA    |

| I <sub>Ave</sub>    | Broadcast Rx @ 0.5Hz in byte sync mode                 |       |     | 7.8  |      | μA    |

| I <sub>Ave</sub>    | Acknowledged @ 0.5Hz in byte sync mode                 |       |     | 12.4 |      | μA    |

| I <sub>Ave</sub>    | Burst continuous @ 14Kbps in byte sync mode            |       |     | 2.24 |      | mA    |

| I <sub>Ave</sub>    | Burst continuous @ 20Kbps in byte sync mode            |       |     | 3.21 |      | mA    |

| I <sub>Ave</sub>    | Burst continuous @ 10Kbps in bit sync mode             |       |     | 3.22 |      | mA    |

| I <sub>Ave</sub>    | Burst continuous @ 14Kbps in Async mode at 57 600 baud |       |     | 2.37 |      | mA    |

| I <sub>Ave</sub>    | Burst continuous @ 20Kbps in Async mode at 57 600 baud |       |     | 3.31 |      | mA    |

|                     | Transmitter operation                                  |       |     |      |      |       |

| P <sub>RF</sub>     | Maximum output power                                   | 2)    |     | 0    | 4    | dBm   |

| ΔΡ                  | Output power variation                                 | 3)    |     |      | ±4   | dBm   |

| P <sub>BW</sub>     | 20dB bandwidth for modulated carrier                   |       |     |      | 1000 | kHz   |

| P <sub>RF2</sub>    | 2 <sup>nd</sup> adjacent channel transmit power 2MHz   |       |     |      | -20  | dBm   |

| P <sub>RF3</sub>    | 3 <sup>rd</sup> adjacent channel transmit power 3MHz   |       |     |      | -40  | dBm   |

| $I_{VCC}$           | Supply peak current @ 0dBm output power                |       |     | 11.3 |      | mA    |

| I <sub>VCC</sub>    | Supply peak current @ -20dBm output power              |       |     | 7    |      | mA    |

|                     | Receiver operation                                     |       |     |      |      |       |

| I <sub>VCC</sub>    | Supply peak current receive mode                       |       |     | 12   |      | mA    |

| RX <sub>SENS</sub>  | Sensitivity at 0.1%BER (@1000kbps)                     |       |     | -85  |      | dBm   |

| C/I <sub>co</sub>   | C/I co-channel                                         |       |     | 9    |      | dB    |

| C/I <sub>1ST</sub>  | 1 <sup>st</sup> adjacent channel selectivity C/I 1MHz  |       |     | 8    |      | dB    |

| C/I <sub>2ND</sub>  | 2 <sup>nd</sup> adjacent channel selectivity C/I 2MHz  |       |     | -22  |      | dB    |

| C/I <sub>3RD</sub>  | 3 <sup>rd</sup> adjacent channel selectivity C/I 3MHz  |       |     | -30  |      | dB    |

1) Usable band is determined by local regulations.

2) Maximum output power with 0dBm output power setting.

3) Variation from 2402MHz to 2479MHz.

4) Voltages exceeding the reference can be used but provide no information.

5) Max refers to total number of samples available to be distributed over the number of A/D sources currently active.

### 2.1 Current Calculation Examples

1. Master channel with Broadcast data at 4Hz with a bit synchronous serial interface.

$I_{ave} = (I_{Msg_Tx_BitSync} * Message_Rate) + I_{Base}$  $= (18.4 \ \mu\text{A}/\text{message} * 4 \ \text{messages}) + 2.6 \ \mu\text{A}$  $= 76.2 \ \mu\text{A}$

2.Receive channel with Acknowledged data at 2Hz with an asynchronous serial interface at 57 600 baud.

12 of 17

AT3 RF Transceiver Chipset, Rev 1.4

$I_{ave} = (I_{Msg_Ack_57600} * Message_Rate) + I_{Base}$  $= (18.7\mu A/message * 2 messages) + 2.6\mu A$  $= 40.0\mu A$

3.Transmit channel with Acknowledged data at 2Hz with an asynchronous serial interface at 57 600 baud.

$I_{ave} = (I_{Msg_{Ack_{57600}}} * Message_{Rate}) + I_{Base}$

= (18.7  $\mu$ A/message \* 2 messages) + 2.6 $\mu$ A

=  $40.0 \mu A$

4.SensRcore device using an ANT message rate of 4Hz and sampling an A/D input at 16 Hz.

```

I_{ave} = (I_{SC_{RF}} * Message_Rate) + (I_{Sample} * Sample_Rate) + I_{Base}= (13\mu A/message * 4 messages) + (0.5\mu A/sample * 16 samples) + 2.6\mu A= 62.6\mu A

```

#### 2.2 A/D Specifications

Note: The Tables in Section 2.2 are obtained from Texas Instruments' datasheet.

|                    | PARAMETER                               | TEST CONDITIONS                                                    | TA           | VCC   | MIN | ТҮР  | MAX             | UNIT |

|--------------------|-----------------------------------------|--------------------------------------------------------------------|--------------|-------|-----|------|-----------------|------|

| V <sub>CC</sub>    | Analog supply voltage<br>range          | V <sub>SS</sub> = 0 V                                              |              |       | 2.2 |      | 3.6             | V    |

| V <sub>Ax</sub>    | Analog input voltage range (see Note 2) | All Ax terminals.<br>Analog inputs selected in<br>ADC10AE register |              |       | 0   |      | V <sub>CC</sub> | V    |

|                    | ADC10 supply current                    | $f_{ADC10CLK} = 5.0 \text{ MHz}$<br>ADC10ON = 1, REFON = 0,        | l: -40–85°C  | 2.2 V |     | 0.52 | 1.05            |      |

| I <sub>ADC10</sub> | (see Note 3)                            | ADC10SHT0 = 1,<br>ADC10SHT1 = 0,<br>ADC10DIV = 0                   | T: -40–105°C | 3 V   |     | 0.6  | 1.2             | mA   |

10-bit ADC, power supply and input range conditions (see Note 1)

## 10-bit ADC, built-in voltage reference

|                      | PARAMETER                                                  | TEST CONDITIONS                                          | VCC       | MIN  | ТҮР | MAX  | UNIT |

|----------------------|------------------------------------------------------------|----------------------------------------------------------|-----------|------|-----|------|------|

| V <sub>CC,REF+</sub> | Positive built-in reference<br>analog supply voltage range | I <sub>VREF+</sub> ≤ 1 mA, REF2_5V = 0                   |           | 2.2  |     |      |      |

|                      |                                                            | I <sub>VREF+</sub> ≤ 0.5 mA, REF2_5V = 1                 |           | 2.8  |     |      | V    |

|                      |                                                            | I <sub>VREF+</sub> ≤ 1 mA, REF2_5V = 1                   |           | 2.9  |     |      |      |

| V <sub>REF+</sub>    | Positive built-in reference voltage                        | I <sub>VREF+</sub> ≤ I <sub>VREF+</sub> max, REF2_5V = 0 | 2.2 V/3 V | 1.41 | 1.5 | 1.59 |      |

|                      |                                                            | I <sub>VREF+</sub> ≤ I <sub>VREF+</sub> max, REF2_5V = 1 | 3 V       | 2.35 | 2.5 | 2.65 | V    |

AT3 RF Transceiver Chipset, Rev 1.4

13 of 17

#### 10-bit ADC, linearity parameters

|                | PARAMETER                    | TEST CONDITIONS                                                                                                                                                              | VCC       | MIN | ТҮР  | MAX | UNIT |

|----------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|------|-----|------|

| EI             | Integral linearity error     |                                                                                                                                                                              | 2.2 V/3 V |     |      | ±1  | LSB  |

| ED             | Differential linearity error |                                                                                                                                                                              | 2.2 V/3 V |     |      | ±1  | LSB  |

| Eo             | Offset error                 | Source impedance $R_S < 100 \Omega$ ,                                                                                                                                        | 2.2 V/3 V |     |      | ±1  | LSB  |

| E <sub>G</sub> |                              | SREFx = 010, unbuffered external reference, $V_{eREF+} = 1.5 V$                                                                                                              | 2.2 V     |     | ±1.1 | ±2  |      |

|                |                              | SREFx = 010, unbuffered external reference, $V_{eREF+} = 2.5 V$                                                                                                              | 3 V       |     | ±1.1 | ±2  |      |

|                | Gain error                   | SREFx = 011, buffered external<br>reference (see Note 1),<br>V <sub>eREF+</sub> = 1.5 V                                                                                      | 2.2 V     |     | ±1.1 | ±4  | LSB  |

|                |                              | SREFx = 011, buffered external reference (see Note 1), $V_{eREF+} = 2.5 V$                                                                                                   | 3 V       |     | ±1.1 | ±3  |      |

| ET             |                              | SREFx = 010, unbuffered external reference, $V_{eREF+}$ = 1.5 V                                                                                                              | 2.2 V     |     | ±2   | ±5  |      |

|                |                              | SREFx = 010, unbuffered external reference, $V_{eREF+} = 2.5 V$                                                                                                              | 3 V       |     | ±2   | ±5  |      |

|                | Total unadjusted error       | SREFx = 011, buffered external reference (see Note 1), $V_{eREF+} = 1.5 V$                                                                                                   | 2.2 V     |     | ±2   | ±7  | LSB  |

|                |                              | $\label{eq:sreen} \begin{array}{l} {\sf SREFx} = 011, \mbox{ buffered external} \\ {\sf reference} \ (see \ Note \ 1), \\ {\sf V}_{e{\sf REF+}} = 2.5 \ {\sf V} \end{array}$ | 3 V       |     | ±2   | ±6  |      |

NOTES: 1. The reference buffer offset adds to the gain and total unadjusted error.

### 10-bit ADC, external reference (see Note 1)

|                     | PARAMETER                                                                                           | TEST CONDITIONS                                                                                                                                                       | VCC       | MIN | TYP | МАХ             | UNIT |

|---------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|-----------------|------|

| V <sub>eREF*</sub>  | Positive external reference input<br>voltage range (see Note 2)                                     | $V_{eREF+} > V_{eREF-}$<br>SREF1 = 1, SREF0 = 0                                                                                                                       |           | 1.4 |     | $v_{\rm CC}$    | v    |

|                     |                                                                                                     | $\label{eq:VeREF} \begin{array}{l} V_{eREF-} \leq V_{eREF+} \leq V_{CC} - 0.15 \ \text{V}, \\ \text{SREF1} = 1, \ \text{SREF0} = 1 \ (\text{see Note 3}) \end{array}$ |           | 1.4 |     | 3.0             |      |

| VeREF-              | Negative external reference input<br>voltage range (see Note 4)                                     | $V_{eREF+} > V_{eREF-}$                                                                                                                                               |           | 0   |     | 1.2             | v    |

| $\Delta V_{eREF}$   | Differential external reference input<br>voltage range<br>$\Delta V_{eREF} = V_{eREF+} - V_{eREF-}$ | V <sub>eREF+</sub> > V <sub>eREF-</sub> (see Note 5)                                                                                                                  |           | 1.4 |     | V <sub>CC</sub> | v    |

| IVeREF+             | Static input current into V <sub>eREF+</sub>                                                        | $\begin{array}{l} 0V \leq V_{eREF+} \leq V_{CC}, \\ SREF1 = 1,  SREF0 = 0 \end{array} \end{array} \label{eq:vertex}$                                                  | 2.2 V/3 V |     |     | ±1              |      |

|                     |                                                                                                     | $\begin{array}{l} 0V \leq \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$                                                                       |           |     |     | 0               | μA   |

| I <sub>VeREF-</sub> | Static input current into VeREF-                                                                    | $0V \le V_{eREF-} \le V_{CC}$                                                                                                                                         | 2.2 V/3 V |     |     | ±1              | μΑ   |

NOTES: 1. The external reference is used during conversion to charge and discharge the capacitance array. The input capacitance, C<sub>1</sub>, is also the dynamic load for an external reference during conversion. The dynamic impedance of the reference supply should follow the recommendations on analog-source impedance to allow the charge to settle for 10-bit accuracy.

The accuracy limits the minimum positive external reference voltage. Lower reference voltage levels may be applied with reduced accuracy requirements.

Under this condition, the external reference is internally buffered. The reference buffer is active and requires the reference buffer supply current I<sub>REFB</sub>. The current consumption can be limited to the sample and conversion period with REBURST = 1.

The accuracy limits the maximum negative external reference voltage. Higher reference voltage levels may be applied with reduced accuracy requirements.

The accuracy limits the minimum external differential reference voltage. Lower differential reference voltage levels may be applied with reduced accuracy requirements.

#### 14 of 17

AT3 RF Transceiver Chipset, Rev 1.4

## **3** Schematics

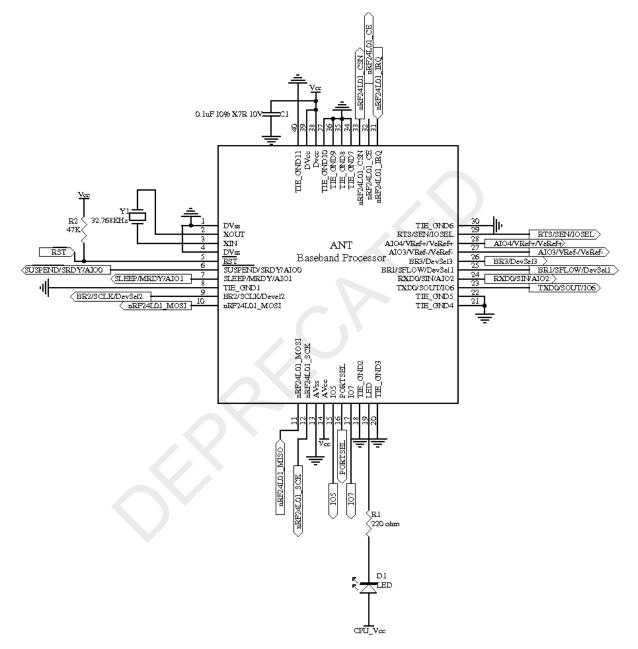

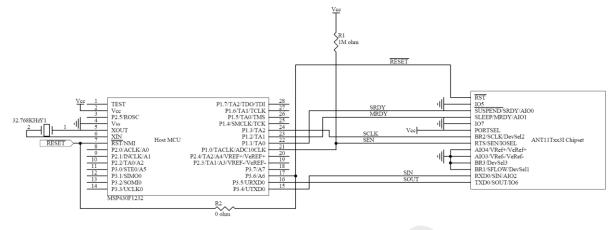

#### 3.1 ANT Baseband Processor Schematic

AT3 RF Transceiver Chipset, Rev 1.4

15 of 17

### 3.2 Interface Examples

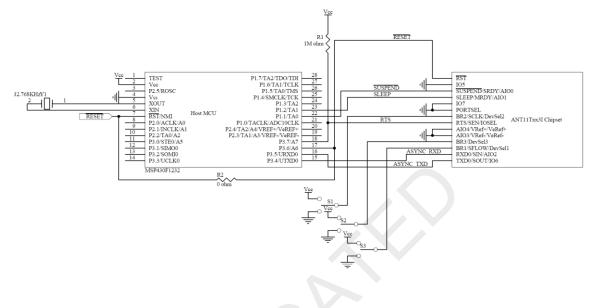

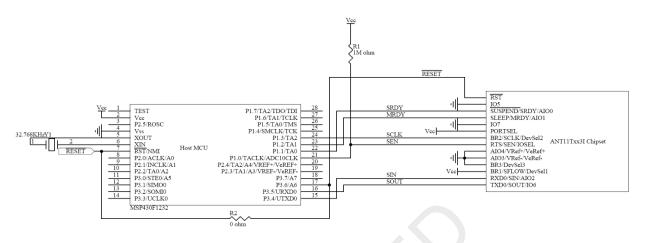

### 3.2.1 Async Mode

#### Notes:

- The ANT chipset's RXD and TXD connected directly to hardware USART of microcontroller.

- The illustrated switches on the baud rate selection pins (BR1, BR2, and BR3) are for ease of use only. The Baud rate selection pins may be connected directly to the logic level of interest.

- R2 allows optional control of the ANT chipset's RESET signal by a microcontroller I/O pin.

#### 16 of 17

AT3 RF Transceiver Chipset, Rev 1.4

### 3.2.2 Byte Sync Mode

#### Notes:

- The ANT chipset's SOUT and SIN connected directly to hardware USART of microcontroller.

- SCLK and SEN need to be on interrupt-capable I/O pins on the microcontroller.

- R3 allows optional control of the ANT chipset's RESET signal by a microcontroller I/O pin.

AT3 RF Transceiver Chipset, Rev 1.4

17 of 17

#### 3.2.3 Bit Sync Mode

#### Notes:

- All interface signals are connected directly to I/O pins on the microcontroller.

- SCLK and SEN need to be on interrupt-capable I/O pins on the microcontroller.

- R3 allows optional control of the ANT chipset's RESET signal by a microcontroller I/O pin.