THIS DOCUMENT IS DEPRECATED AND PROVIDED "AS IS" WITH NO SUPPORT FROM THE ANT TEAM.

USE IS AT THE SOLE DISCRETION OF THE USER.

D00001452 Rev 1.0

Page 2 of 5 AT3 Chipset Errata, Rev 1.0

# **Copyright Information and Usage Notice**

This information disclosed herein is the exclusive property of Dynastream Innovations Inc. No part of this publication may be reproduced or transmitted in any form or by any means including electronic storage, reproduction, execution or transmission without the prior written consent of Dynastream Innovations Inc. The recipient of this document by its retention and use agrees to respect the copyright of the information contained herein.

The information contained in this document is subject to change without notice and should not be construed as a commitment by Dynastream Innovations Inc. unless such commitment is expressly given in a covering document.

The Dynastream Innovations Inc. ANT Products described by the information in this document are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Dynastream product could create a situation where personal injury or death may occur. If you use the Products for such unintended and unauthorized applications, you do so at your own risk and you shall indemnify and hold Dynastream and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Dynastream was negligent regarding the design or manufacture of the Product.

©2011 Dynastream Innovations Inc. All Rights Reserved.

AT3 Chipset Errata, Rev 1.0

Page 3 of 5

# **Table of Contents**

| 1 | Chipset Revision |                                    | 4 |

|---|------------------|------------------------------------|---|

|   | 1.1              | ANT MCU Tracking Code              | 4 |

|   | 1.2              | Package Label                      | 4 |

|   | 1.3              | Version String                     | 4 |

| 2 | Known Issues     |                                    | 5 |

|   | 2.1              | Multiple Channel Collision         | 5 |

|   | 2.2              | Initialization Issue After a Reset | 5 |

Page 4 of 5 AT3 Chipset Errata, Rev 1.0

This document describes the known exceptions to the datasheet of AT3 chipsets. Workarounds or fixes are provided.

# 1 Chipset Revision

The AT3 chipsets contains two chips, an ANT MCU and an Radio IC nRF24L01 or L01P from Nordic Semiconductor. The chipset revision refers to the firmware version loaded to the ANT MCU. It can be identified in the following ways.

# 1.1 ANT MCU Tracking Code

Each AT3 MCU has a 4 character tracking code printed on the product sticker. The third character denotes the revision. The picture shows that the ANT MCU is rev B.

# 1.2 Package Label

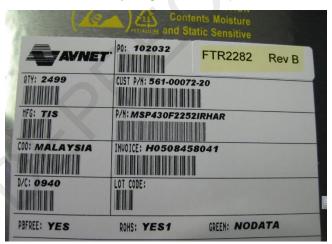

For sealed reels, the revision is marked on the package Label as below

### 1.3 Version String

In the case that the chip sticker is hard to access or identification marker is blurred, an ANT version command 0x3E can be issued via the serial communication to acquire the version String.

| Revision | Version String          |

|----------|-------------------------|

| В        | AGC1.05Cxx <sup>1</sup> |

| Α        | AGC1.04Cxx <sup>1</sup> |

Note 1: "xx" denotes the different AT3 model. For the 8 channel, non-SensRcore FTR2282, it shows 'AD"

AT3 Chipset Errata, Rev 1.0 Page 5 of 5

### 2 Known Issues

## 2.1 Multiple Channel Collision

Rev A is affected. This issue has been fixed in rev B and above

#### Symptoms:

Having multiple channels on a single device with at least one master can cause prolonged blocked channel events and in some cases a channel outage of 2 seconds or more resulting in long data outages or searches on the slave device.

# **Conditions:**

Channels of different message rates are opened on the same device, one being a master channel. The message rates are not synchronous relative to each other and thus collide over time.

#### Consequences:

Channel collision is unavoidable in this case of multiple channels at different message rate. But the issue causes higher than normal failures. In some instances, this causes a 2 second outage for a master channel, which can result in the slave device dropping to search.

#### Workaround:

If the multi-channel scenario is one master and some number of slaves, using channel 0 for the master channel can mitigate the issue.

### 2.2 Initialization Issue After a Reset

Both rev A and Rev B are affected. This issue will be fixed in rev C

### Symptoms:

The AT3 chipset sometimes fails to initialize after a reset.

#### **Conditions:**

This issue is seen when an external clock source is used. Failure points can vary from chip to chip.

The issue does not appear when using a crystal as the clock.

### **Consequences:**

Chipset may fail to initialize sporadically after a reset.

#### Workaround:

Use the RESET pin to reset the chipset, and retry the reset sequence if the AT3 fails to initialize properly after a reset. A successful initialization can be confirmed by observing the AT3 lowering RTS within 500ms of a reset. The phase of the reset pulse with respect to the external clock source should be different in each reset retry attempt.