#

# **SoftDevice Specification**

# S212 SoftDevice v2.0

# **Copyright Information and Usage Notice**

This information disclosed herein is the exclusive property of Dynastream Innovations Inc. and Nordic Semiconductor ASA. No part of this publication may be reproduced or transmitted in any form or by any means including electronic storage, reproduction, execution or transmission without the prior written consent of Dynastream Innovations Inc. The recipient of this document by its retention and use agrees to respect the copyright of the information contained herein.

The information contained in this document is subject to change without notice and should not be construed as a commitment by Dynastream Innovations Inc. unless such commitment is expressly given in a covering document.

The Dynastream Innovations Inc. ANT Products described by the information in this document are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Dynastream product could create a situation where personal injury or death may occur. If you use the Products for such unintended and unauthorized applications, you do so at your own risk and you shall indemnify and hold Dynastream and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Dynastream was negligent regarding the design or manufacture of the Product.

©2016 Dynastream Innovations Inc. All Rights Reserved.

# **Revision History**

| Revision | Effective Date | Description                          |

|----------|----------------|--------------------------------------|

| 1.0      | June 2016      | Initial SDS creation                 |

| 2.0      | September 2016 | High Duty Search and Time Sync added |

|          |                |                                      |

|          |                |                                      |

|          |                |                                      |

|          |                |                                      |

|          |                |                                      |

|          |                |                                      |

# **Table of Contents**

| 1  | <b>S21</b> | S212 SoftDevice |                                                               |    |  |

|----|------------|-----------------|---------------------------------------------------------------|----|--|

| 2  | Doc        | umentatio       | )n                                                            | 9  |  |

| 3  | Proc       | duct Overv      | /iew                                                          | 10 |  |

| 4  | Арр        | lication Pr     | ogramming Interface (API)                                     | 11 |  |

|    | 4.1        | Events -        | - SoftDevice to application                                   | 11 |  |

|    | 4.2        | Error ha        | ndling                                                        | 11 |  |

| 5  | Soft       | Device Ma       | anager                                                        | 12 |  |

|    | 5.1        | SoftDevi        | ice enable and disable                                        | 12 |  |

|    |            | 5.1.1           | ANT License Key                                               | 12 |  |

|    | 5.2        | Clock so        | purce                                                         | 12 |  |

|    | 5.3        | Power m         | nanagement                                                    | 13 |  |

|    | 5.4        | Memory          | isolation and runtime protection                              | 13 |  |

| 6  | Syst       | tem on Chi      | ip (SoC) Library                                              | 16 |  |

| 7  | Syst       | tem on Chi      | ip resource requirements                                      | 17 |  |

|    | 7.1        | Hardwar         | re peripherals                                                | 17 |  |

|    | 7.2        | Applicat        | ion signals – Software Interrupts (SWI)                       | 20 |  |

|    | 7.3        | Program         | nmable Peripheral Interconnect (PPI)                          | 21 |  |

|    | 7.4        | SVC nur         | nber ranges                                                   | 22 |  |

|    | 7.5        | Peripher        | ral runtime protection                                        | 22 |  |

|    | 7.6        | External        | l and miscellaneous requirements                              | 22 |  |

| 8  | Flas       | h memory        | / API                                                         | 23 |  |

|    | 8.1        | Using fla       | ash with ANT activity                                         | 23 |  |

| 9  | Mult       | tiprotocol      | support                                                       | 24 |  |

|    | 9.1        | Non-con         | ncurrent multiprotocol implementation                         | 24 |  |

|    | 9.2        | Concurre        | ent multiprotocol implementation using the Radio Timeslot API | 24 |  |

|    |            | 9.2.1           | Request types                                                 | 24 |  |

|    |            | 9.2.2           | Request priorities                                            | 24 |  |

|    |            | 9.2.3           | Timeslot length                                               | 25 |  |

|    |            | 9.2.4           | Scheduling                                                    | 25 |  |

|    |            | 9.2.5           | Performance considerations                                    | 25 |  |

|    |            | 9.2.6           | Radio Timeslot API                                            | 26 |  |

|    | 9.3        | Radio Ti        | imeslot API usage scenarios                                   | 28 |  |

|    |            | 9.3.1           | Complete session example                                      | 28 |  |

|    |            | 9.3.2           | Blocked timeslot scenario                                     | 29 |  |

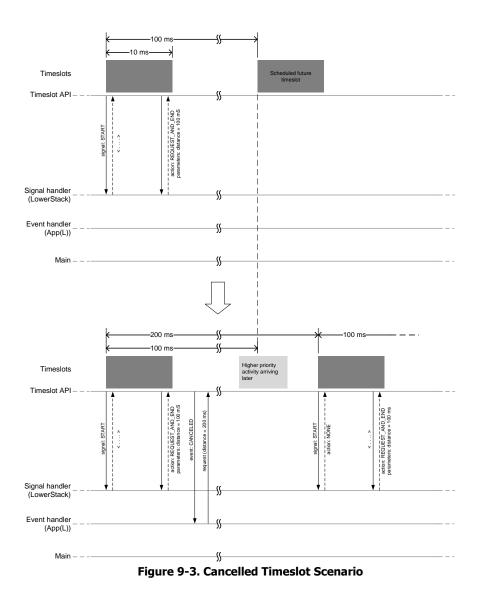

|    |            | 9.3.3           | Cancelled timeslot scenario                                   | 30 |  |

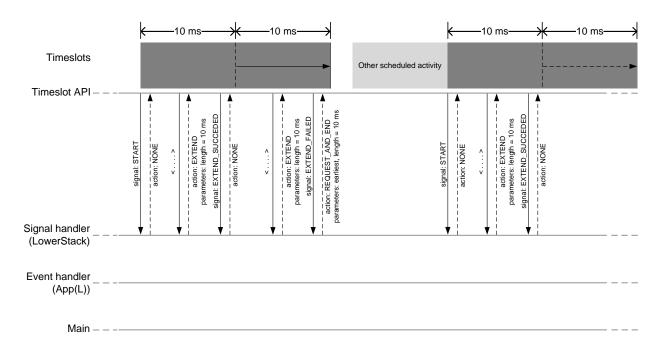

|    |            | 9.3.4           | Radio Timeslot extension example                              | 31 |  |

| 10 | ANT        | Protocol        | Stack                                                         | 32 |  |

|    | 10.1       | Over            | view                                                          | 32 |  |

|    | 10.2         | ANT f      | eature support                                                     | . 32 |

|----|--------------|------------|--------------------------------------------------------------------|------|

|    |              | 10.2.1     | Search Uplink                                                      | . 32 |

|    |              | 10.2.2     | Group Transmitter Initiation                                       | . 32 |

|    |              | 10.2.3     | High Duty Search                                                   | . 33 |

|    |              | 10.2.4     | Time Sync                                                          | . 33 |

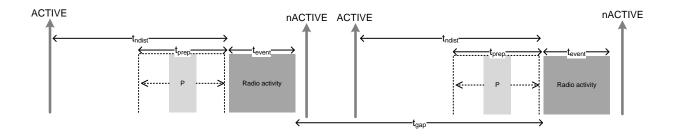

| 11 | Radi         | o Notifica | tion                                                               | . 34 |

|    | 11.1         | Radio      | Notification Signals                                               | . 34 |

|    | 11.2         | ANT t      | raffic Radio Notifications                                         | . 36 |

|    |              | 11.2.1     | ANT Broadcast traffic                                              |      |

|    |              | 11.2.2     | ANT Burst traffic                                                  | . 37 |

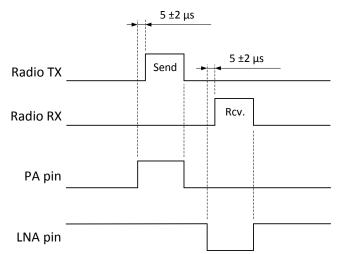

|    | 11.3         |            | r Amplifier and Low Noise Amplifier control configuration (PA/LNA) |      |

| 12 | Mast         | er Boot R  | ecord and bootloader                                               | . 41 |

|    | 12.1         | Maste      | er Boot Record                                                     | . 41 |

|    | 12.2         |            | pader                                                              |      |

|    | 12.3         |            | er Boot Record (MBR) and SoftDevice reset procedure                |      |

|    | 12.4         |            | er Boot Record (MBR) and SoftDevice initialization procedure       |      |

| 13 |              |            | ormation structure                                                 |      |

| 14 | Soft         |            | mory usage                                                         |      |

|    | 14.1         |            | pry resource map and usage                                         |      |

|    |              | 14.1.1     | Memory resource requirements                                       |      |

|    | 14.2         |            | Channel Configuration                                              |      |

| 15 |              | -          |                                                                    |      |

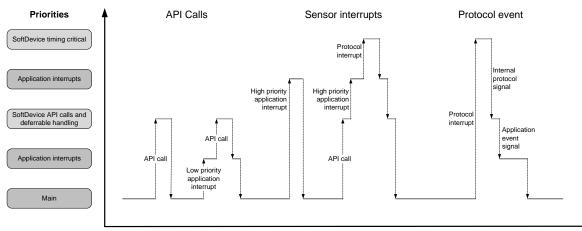

|    | 15.1         |            | evice timing-activities and priorities                             |      |

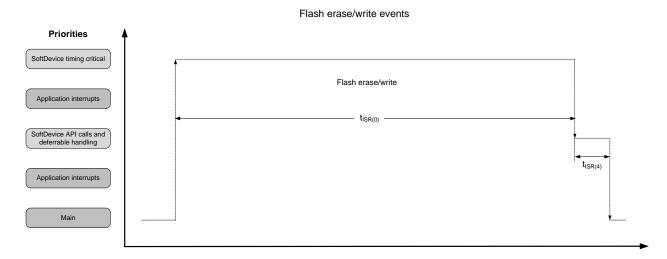

|    | 15.2         |            | API timing                                                         |      |

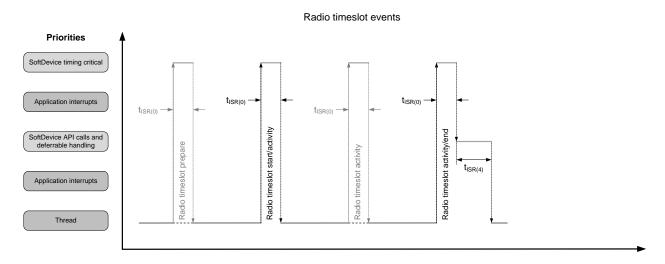

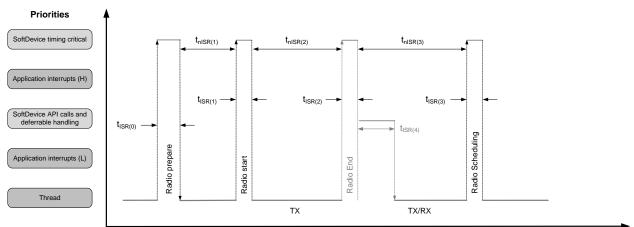

|    | 15.3         |            | slot API timing                                                    |      |

| 16 |              | -          | el and processor availability                                      |      |

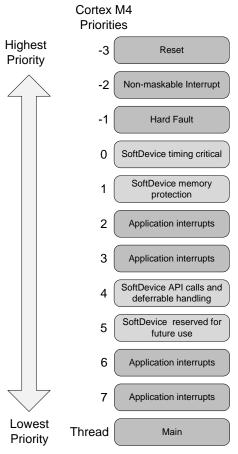

|    | 16.1         | •          | btion model                                                        |      |

|    |              | 16.1.1     | Interrupt forwarding to the application                            |      |

|    | 16.0         | 16.1.2     | Interrupt latency due to System on Chip (SoC) framework            |      |

|    | 16.2<br>16.3 |            | upt priority levels<br>ssor usage patterns and availability        |      |

|    | 10.5         | 16.3.1     | Flash API processor usage patterns                                 |      |

|    |              | 16.3.2     | Radio Timeslot API processor usage patterns                        |      |

|    |              | 16.3.3     | ANT processor usage patterns                                       |      |

|    |              | 16.3.4     | Interrupt latency when using multiple modules and channels         |      |

| 17 | ANT          |            | files                                                              |      |

| _, | 17.1         | • •        | er Channel                                                         |      |

|    | 17.2         |            | Channel                                                            |      |

| 18 | Soft         |            | ntification and revision scheme                                    |      |

|    | 18.1         | MBR        | distribution and revision scheme                                   | . 62 |

|    |              |            |                                                                    |      |

# List of Figures

| Figure 3-1. System on Chip application with the SoftDevice                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-1. Memory region designation 14                                                                                         |

| Figure 9-1. Complete Radio Timeslot session example                                                                              |

| Figure 9-2. Blocked timeslot scenario                                                                                            |

| Figure 9-3. Cancelled Timeslot Scenario                                                                                          |

| Figure 9-4. Radio Timeslot Extension Example                                                                                     |

| Figure 10-1. ANT Stack Architecture                                                                                              |

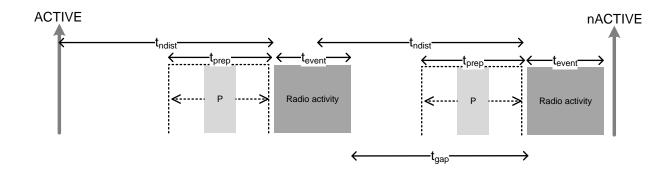

| Figure 11-1. Two Radio Events with ACTIVE and nACTIVE Signals                                                                    |

| Figure 11-2. Two radio events where $t_{gap}$ is too small and the notification signals will not be available between the events |

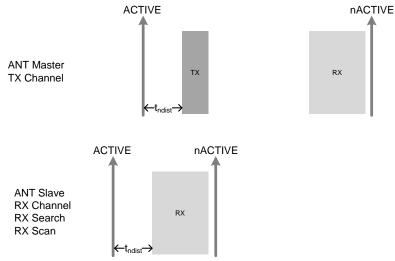

| Figure 11-3. ANT Broadcast with $t_{ndist}$ >= 1740 $\mu s$                                                                      |

| Figure 11-4. ANT Broadcast with $t_{\text{ndist}}$ = 800 $\mu s$                                                                 |

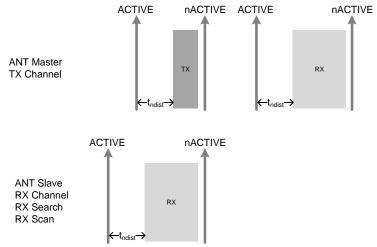

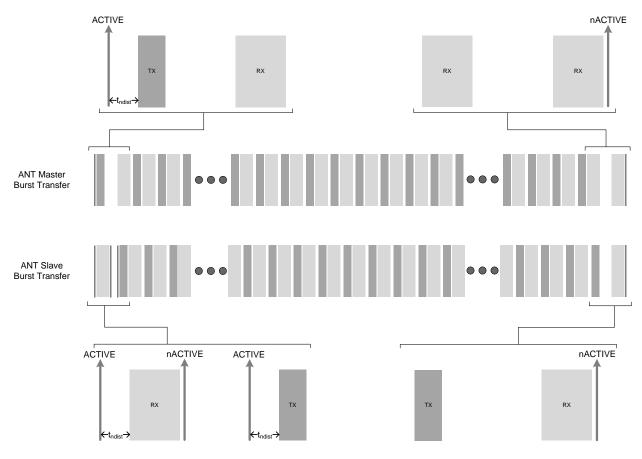

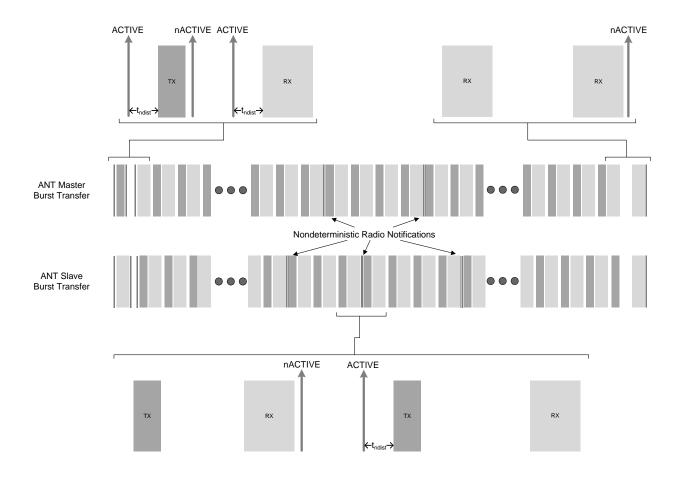

| Figure 11-5. ANT Burst with $t_{ndist}$ >= 2680 $\mu s$                                                                          |

|                                                                                                                                  |

| Figure 11-6. ANT Burst with ndist = 1740µs                                                                                       |

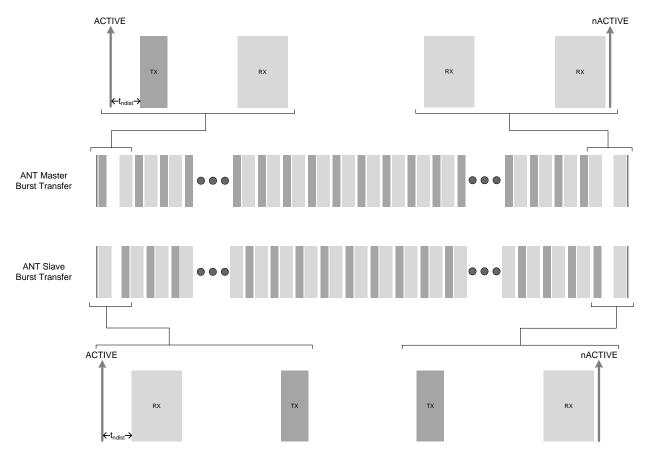

| Figure 11-6. ANT Burst with ndist = 1740µs38Figure 11-7. ANT Burst with ndist = 800µs39                                          |

|                                                                                                                                  |

| Figure 11-7. ANT Burst with ndist = 800µs                                                                                        |

| Figure 11-7. ANT Burst with ndist = 800µs                                                                                        |

| Figure 11-7. ANT Burst with ndist = 800µs                                                                                        |

| Figure 11-7. ANT Burst with ndist = 800µs                                                                                        |

| Figure 11-7. ANT Burst with ndist = 800µs                                                                                        |

| Figure 11-7. ANT Burst with ndist = 800µs                                                                                        |

| Figure 11-7. ANT Burst with ndist = 800µs                                                                                        |

| Figure 11-7. ANT Burst with ndist = 800µs                                                                                        |

| Figure 11-7. ANT Burst with ndist = 800µs                                                                                        |

# **List of Tables**

| Table 1-1. Summary of key features and applications                                | 8    |

|------------------------------------------------------------------------------------|------|

| Table 2-1. S212 SoftDevice core documentation                                      | 9    |

| Table 6-1. System on Chip features                                                 | . 16 |

| Table 7-1. Hardware access type definitions                                        | . 17 |

| Table 7-2. Peripheral protection and usage by SoftDevice                           | . 17 |

| Table 7-3. Allocation of Software Interrupt vectors to SoftDevice signals          | . 20 |

| Table 7-4. Assigning PPI channels between the application and SoftDevice           | . 21 |

| Table 7-5. Assigning preprogrammed channels between the application and SoftDevice | . 21 |

| Table 7-6. Assigning PPI groups between the application and SoftDevice             | . 21 |

| Table 7-7. SVC number allocation                                                   | . 22 |

| Table 8-1. Behaviour with ANT traffic and concurrent flash write/erase         23    |

|--------------------------------------------------------------------------------------|

| Table 9-1. API calls                                                                 |

| Table 9-2. Radio Timeslot events    26                                               |

| Table 9-3. Radio Timeslot signals                                                    |

| Table 9-4. Signal handler action return values    27                                 |

| Table 11-1. Notation and terminology for the Radio Notification used in this chapter |

| Table 14-1. S212 Memory resource requirements for flash    46                        |

| Table 14-2. S212 Memory resource requirements for RAM    46                          |

| Table 14-3. S212 Memory resource requirements for call stack    47                   |

| Table 15-1. Scheduling priorities    48                                              |

| Table 16-1. Additional latency due to SoftDevice and MBR forwarding interrupts       |

| Table 16-2. Processor usage for the flash API                                        |

| Table 16-3. Processor usage for the Radio Timeslot API                               |

| Table 16-4. Processor usage latency when connected (ANT)    56                       |

| Table 16-5. Processor idle time for ANT traffic                                      |

| Table 17-1. Master Channel power usage breakdown    58                               |

| Table 17-2. Slave Channel power usage breakdown    59                                |

| Table 18-1. Revision scheme    61                                                    |

| Table 18-2. SoftDevice revision examples                                             |

| Table 18-3. Test qualification levels    62                                          |

# 1 S212 SoftDevice

The S212 SoftDevice is an ANT protocol stack solution. The S212 SoftDevice integrates an ANT Master/Slave stack and provides a complete API that allows up to 15 channels and can be configured into a flexible network solution that covers everything from point-to-point to mesh networks. The S212 SoftDevice is designed for use with the nRF52 System on Chip (SoC) solutions.

| Key features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>ANT compliant low energy wireless communications</li> <li>Simple to complex network topologies supported</li> <li>Logical channels individually configurable for channel type, ID, period, RF frequency, and network</li> <li>Broadcast, acknowledged or burst data transfer</li> <li>Device search, pairing, and proximity support</li> <li>8 byte data payload per message</li> <li>Advanced ANT Features:         <ul> <li>Configurable for up to 15 ANT channels</li> <li>AES-128 data encryption option for data transfers on all ANT channels</li> <li>Advanced Burst Transfer mode (up to 60 kbps)</li> <li>Up to 8 public, managed, and/or private ANT network keys</li> <li>Event Filtering and Selective Data Updates</li> <li>Asynchronous Transmission</li> <li>Fast Channel Initiation</li> <li>Search Uplink</li> <li>Group Transmitter Initiation</li> <li>High Duty Search</li> <li>Time Sync</li> </ul> </li> <li>Master Boot Record for over-the-air device firmware update</li> <ul> <li>ANT updater available</li> <li>SoftDevice, application, and bootloader can be updated separately</li> </ul> <li>Memory isolation between the application and the protocol stack for robustness and security</li> <li>Thread-safe supervisor-call based API</li> <li>Asynchronous, event-driven behaviour</li> <li>No RTOS dependency</li> <li>Any RTOS can be used</li> <li>No link-time dependencies</li> <li>Standard ARM® Cortex®-M4 project configuration for application development</li> <li>Support for concurrent and non-concurrent multiprotocol operation</li> <li>Concurrent with the ANT stack using the Radio Timeslot API</li> <li>Alternate protocol stack in application space</li> <li>Support for control of external Power Amplifiers and Low Noise Amplifiers</li> </ul> | <ul> <li>Sports and fitness devices <ul> <li>Sports watches</li> <li>Bike computers</li> <li>Wearables</li> </ul> </li> <li>Personal Area Networks <ul> <li>Health and fitness sensor and monitoring devices</li> <li>Medical devices</li> <li>Key fobs and wrist watches</li> </ul> </li> <li>Home automation</li> <li>Remote control toys</li> <li>Computer peripherals and I/O devices <ul> <li>Mice</li> <li>Keyboards</li> <li>Multi-touch trackpads</li> </ul> </li> <li>Interactive entertainment devices <ul> <li>Gaming controllers</li> <li>Environment sensor networks</li> <li>High density networking and monitoring</li> <li>Logistics and goods tracking</li> <li>Smart RF tags</li> <li>Internet of Things</li> </ul> </li> </ul> |

#### Table 1-1. Summary of key features and applications

# 2 Documentation

Additional recommended reading for developing applications using the SoftDevice on the nRF52 SoC is listed in Table 2-1. These documents can be downloaded from <u>www.thisisant.com</u>, and <u>www.infocenter.nordicsemi.com</u>.

| Table | 2-1. 5 | 5212 So | ftDevice | core | documentation | on |

|-------|--------|---------|----------|------|---------------|----|

|       |        |         |          |      |               |    |

| Documentation                             | Description                                                                                                                                                                                                                |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nRF52832 Product Specification            | Contains a description of the hardware, peripherals, and electrical specifications specific to the nRF52832 IC.                                                                                                            |

| nRF52832 Errata                           | Contains information on anomalies related to the nRF52832 IC.                                                                                                                                                              |

| nRF52 Series Compatibility Matrix         | Contains information on the compatibility between nRF52 Integrated Circuit (IC) revisions, SoftDevices and SoftDevice Specifications, SDKs, development kits, documentation, and Qualified Design Identifications (QDIDs). |

| ANT Message Protocol and Usage            | Contains information on ANT serial messages and ANT usage                                                                                                                                                                  |

| Nordic S210 SoftDevice Specification v3.0 | Contains information on ANT features and APIs for previous ANT SoftDevice                                                                                                                                                  |

# **3** Product Overview

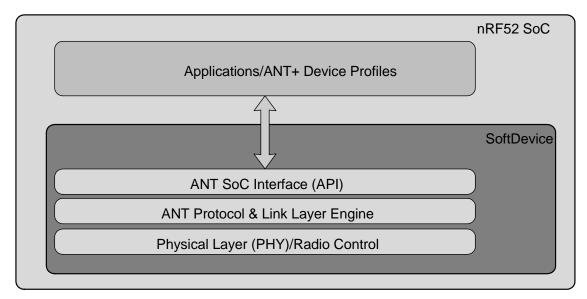

The S212 SoftDevice is a precompiled and linked binary image implementing an ANT protocol stack for the nRF52 Series of SoCs.

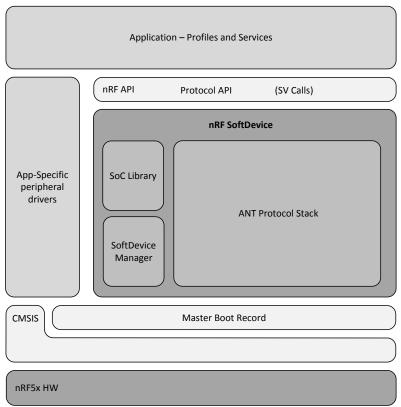

Figure 3-1. System on Chip application with the SoftDevice

Figure 3-1 is a block diagram of the nRF52 series software architecture. It includes the standard ARM<sup>®</sup> CMSIS interface for nRF52 hardware, a master boot record, profile and application code, application specific peripheral drivers, and a firmware module identified as a SoftDevice.

A SoftDevice consists of four main components:

- SoC Library Implementation and nRF API for shared hardware resource management (application coexistence).

- SoftDevice Manager Implementation and nRF API for SoftDevice management (enabling/disabling the SoftDevice, etc.).

- ANT protocol stack Implementation of ANT protocol stack and API.

Each Application Programming Interface (API) is a set of standard C language functions and data types, which are provided as a series of header files. These give the application complete compiler and linker independence from the SoftDevice implementation. See section 4 for more details.

The SoftDevice enables the application developer to develop their code as a standard ARM<sup>®</sup> Cortex<sup>®</sup> -M4 project without having the need to integrate with proprietary IC vendor software frameworks. This means that any ARM<sup>®</sup> Cortex<sup>®</sup> -M4-compatible toolchain can be used to develop ANT applications with the SoftDevice.

The SoftDevice can be programmed onto compatible nRF52 Series ICs during both development and production.

# 4 Application Programming Interface (API)

The SoftDevice Application Programming Interface (API) is available to applications as a C programming language interface based on SuperVisor Calls (SVC) and defined in a set of header files.

In addition to a Protocol API enabling wireless applications, there is an nRF API that exposes the functionality of both the SoftDevice Manager and the SoC Library.

**Important:** When the SoftDevice is disabled, only a subset of the SoftDevice API is available to the application (see S212 SoftDevice v1.0.2 API). For more information about enabling and disabling the SoftDevice, see section 5.1.

SVCs are software triggered interrupts conforming to a procedure call standard for parameter passing and return values. Each SoftDevice API call triggers an SVC interrupt. The SoftDevice SVC interrupt handler locates the correct SoftDevice function, allowing applications to compile without any API function address information at compile time. This removes the necessity for the application to link to the SoftDevice. The header files contain all information required for the application to invoke the API functions with standard programming language prototypes. This SVC interface makes SoftDevice API calls thread-safe; they can be invoked from the application's different priority levels without additional synchronization mechanisms.

**Important:** SoftDevice API functions can only be called from a lower interrupt priority level (higher numerical value for the priority level) than the SVC priority. For more information, see section 16.2.

# 4.1 Events – SoftDevice to application

Software triggered interrupts in a reserved IRQ are used to signal events from the SoftDevice to the application. The application is then responsible for handling the interrupt and for invoking the relevant SoftDevice functions to obtain the event data.

For details on how to implement the handling of these events, see the nRF5 Software Development Kit (nRF5 SDK) documentation available at <u>www.nordicsemi.com</u>.

# 4.2 Error handling

All SoftDevice API functions return a 32-bit error code. The application must check this error code to confirm whether a SoftDevice API function call was successful.

Unrecoverable failures (faults) detected by the SoftDevice will be reported to the application by a registered, fault handling callback function. A pointer to the fault handler must be provided by the application upon SoftDevice initialization. The fault handler is then used to notify of unrecoverable errors and the type of error is indicated as a parameter through the fault handler.

The following types of faults can be reported to the application through the fault handler:

- SoftDevice assertions.

- Attempts by the application to perform illegal memory accesses, either against SoftDevice memory protection rules or to protected peripheral configuration registers at runtime.

The fault handler callback is invoked by the SoftDevice in HardFault context, with all interrupts disabled.

# 5 SoftDevice Manager

The SoftDevice Manager (SDM) API allows the application to control the SoftDevice state and configure the behaviour of certain SoftDevice core functionality.

When enabling the SoftDevice, the SDM configures the following:

- The low frequency clock (LFCLK) source (section 5.2).

- The interrupt management (section5.1).

- The embedded protocol stack.

In addition, it enables the SoftDevice RAM and peripheral protection. See section 5.4.

Detailed documentation of the SDM API is made available with the Software Development Kits (SDK).

#### 5.1 SoftDevice enable and disable

When the SoftDevice is not enabled, the Protocol API and parts of the SoC Library API are not available to the application.

When the SoftDevice is not enabled, most of the SoCs resources are available to the application. However, the following restrictions apply:

- SVC numbers 0x10 to 0xFF are reserved.

- SoftDevice program (flash) memory is reserved.

- A few bytes of RAM are reserved (section 14.1)

Once the SoftDevice has been enabled, more restrictions apply:

- Some RAM will be reserved (section 5.4)

- Some peripherals will be reserved (section 7.1).

- Some of the peripherals that are reserved will have a SoC Library interface.

- Interrupts from the reserved SoftDevice peripherals will not be forwarded to the application (section 16.1.1).

- The reserved peripherals are reset upon SoftDevice disable.

- nrf\_nvic\_ functions must be used instead of CMSIS NVIC\_ functions for safe use of the SoftDevice.

- SoftDevice activity in high priority levels may interrupt the application, increasing the maximum interrupt latency (section 16).

# 5.1.1 ANT License Key

The S332 SoftDevice requires a license key in order to operate. An evaluation key is included in the SoftDevice which will enable the full stack and is to be used for NON-COMMERCIAL USE ONLY. Further information about the license key and/or obtaining a commercial license key can be found at: <a href="http://www.thisisant.com/developer/ant/licensing">www.thisisant.com/developer/ant/licensing</a>.

License validation may cause the enable time of the SoftDevice to extend by up to 100 ms in some configurations.

# 5.2 Clock source

The SoftDevice can use one of two available low frequency clock sources: the internal RC Oscillator, or an external Crystal Oscillator.

The application must provide the selected clock source and some clock source characteristics, such as accuracy, when it enables the SoftDevice. The SoftDevice Manager is responsible for configuring the low frequency clock source and for keeping it calibrated, when the RC oscillator is the selected clock source.

If the SoftDevice is configured with the internal RC oscillator clock option, clock calibration is required periodically and when a temperature change of more than 0.5°C has occurred, to adjust the RC oscillator frequency. See the nRF52832 Product Specification for more information. The SoftDevice will perform this function automatically. The application may choose how often the SoftDevice will make a measurement to detect temperature change based on how frequently significant temperature changes are expected to occur in the intended environment of the end product. A temperature polling interval of 4 seconds and a forced clock calibration every second interval (8 seconds) is recommended (.ctiv=32, .temp\_ctiv=2).

# 5.3 Power management

The SoftDevice implements a simple to use SoftDevice Power API for optimized power management.

The application shall use this API when the SoftDevice is enabled to ensure correct function. When the SoftDevice is disabled, the application must use the hardware abstraction (CMSIS) interfaces for power management.

When waiting for application events using the Power API, the CPU goes to an IDLE state whenever the SoftDevice is not using the CPU. Interrupts handled directly by the SoftDevice do not wake the application. Application interrupts will wake the application as expected. When going to system OFF, the Power API ensures the SoftDevice services are stopped before powering down.

# 5.4 Memory isolation and runtime protection

The SoftDevice data memory and peripherals can be sandboxed and runtime protected to prevent the application from interfering with the SoftDevice execution, ensuring robust and predictable performance.

Sandboxing<sup>1</sup> and runtime protection can allow memory access violations to be detected at development time. This ensures that developed applications will not inadvertently interfere with the correct functioning of the SoftDevice.

Sandboxing is enabled by default when the SoftDevice is enabled and disabled when the SoftDevice is disabled. When enabled, SoftDevice RAM and peripheral registers are protected against write access by the application. The application will have read access to SoftDevice RAM and peripheral registers.

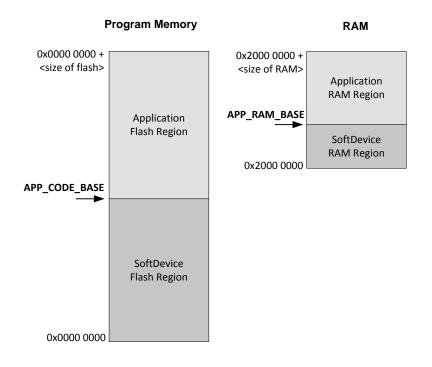

The flash memory is divided into two regions at compile time. The SoftDevice Flash Region is located between addresses 0x0000000 and APP\_CODE\_BASE - 1 and is occupied by the SoftDevice. The Application Flash Region is located between the addresses APP\_CODE\_BASE and the last valid address in the flash memory and is available to the application.

The RAM is also split into two regions, which are defined at runtime, when the SoftDevice is enabled. The SoftDevice RAM Region is located between the addresses  $0 \times 20000000$  and APP\_RAM\_BASE - 1 and is used by the SoftDevice. The Application RAM Region is located between the addresses APP\_RAM\_BASE and the top of RAM and is available to the application.

<sup>&</sup>lt;sup>1</sup> A sandbox is a set of memory access restrictions imposed on the application

#### Figure 5-1 presents an overview of the regions.

Figure 5-1. Memory region designation

The SoftDevice uses a fixed amount of flash (program) memory. By contrast, the size of the SoftDevice RAM Region depends on whether the SoftDevice is enabled.

The amount of flash and RAM available to the application is determined by region size (kilobytes or bytes) and the base addresses of the application code and RAM: APP\_CODE\_BASE and APP\_RAM\_BASE respectively. The application code must be located between APP\_CODE\_BASE and <size of flash>. The application variables must be allocated in an area inside the Application RAM Region, located between APP\_RAM\_BASE and <size of RAM>. This area shall not overlap with the allocated RAM space for the call stack and heap, which is also located inside the Application RAM Region.

Example of an application program's code address range:

APP\_CODE\_BASE ≤ Program ≤ <size of flash>

Example application RAM address range assuming call stack and heap location as shown in Figure 14-1:

APP\_RAM\_BASE ≤ RAM ≤ (0x2000 0000 + <size of RAM>) - (<Call Stack> + <Heap>)

Sandboxing protects the SoftDevice RAM Region so that it cannot be written to by the application at runtime. Violation of sandboxing rules, for example an attempt to write to the protected SoftDevice memory, will result in the triggering of a fault (unrecoverable error handled by the application). See section 4.2 for more information.

When the SoftDevice is disabled, all RAM, with the exception of a few bytes, is available to the application. See section 14.1 for more details. When the SoftDevice is enabled, RAM up to APP\_RAM\_BASE will be used by the SoftDevice and will be write protected.

The typical location of the call stack for an application using the SoftDevice is in the upper part of the Application RAM Region, so the application can place its variables from the end of the SoftDevice RAM Region (APP\_RAM\_BASE) to the beginning of the call stack space.

#### Important:

- The location of the call stack is communicated to the SoftDevice through the contents of the Main Stack Pointer (MSP) register.

- Do not change the value of MSP dynamically (i.e. never set the MSP register directly).

- The RAM located in the SoftDevice RAM Region will be overwritten once the SoftDevice is enabled.

- The SoftDevice RAM Region will be not be cleared or restored to default values after disabling the SoftDevice, so the application must treat the contents of the region as uninitialized memory.

# 6 System on Chip (SoC) Library

The coexistence of Application and SoftDevice with safe sharing of common System on Chip (SoC) resources is ensured by the SoC Library.

The features described in Table 6-1 are implemented by the SoC Library and can be used for accessing the shared hardware resources.

| Table 6 | 5-1. Sy | /stem | on | Chip | features |

|---------|---------|-------|----|------|----------|

|---------|---------|-------|----|------|----------|

| Feature             | Description                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mutex               | The SoftDevice implements atomic mutex acquire and release operations<br>that are safe for the application to use. Use this mutex to avoid disabling<br>global interrupts in the application, because disabling global interrupts<br>will interfere with the SoftDevice and may lead to dropped packets or lost<br>connections.                                            |

| NVIC                | Wrapper functions for the CMSIS NVIC functions provided by ARM <sup>®</sup> .<br><b>Important:</b> To ensure reliable usage of the SoftDevice you must use the wrapper functions when the SoftDevice is enabled.                                                                                                                                                           |

| Rand                | Provides random numbers from the hardware random number generator.                                                                                                                                                                                                                                                                                                         |

| Power               | <ul> <li>Access to power block configuration while the SoftDevice is enabled:</li> <li>Access to RESETREAS register</li> <li>Set power modes</li> <li>Configure power fail comparator</li> <li>Control RAM block power</li> <li>Use general purpose retention register</li> <li>Configure DC/DC converter state: <ul> <li>DISABLED</li> <li>ENABLED</li> </ul> </li> </ul> |

| Clock               | Access to clock block configuration while the SoftDevice is enabled.<br>Allows the HFCLK Crystal Oscillator source to be requested by the<br>application.                                                                                                                                                                                                                  |

| Wait for event      | Simple power management call for the application to use to enter a sleep or idle state and wait for an application event.                                                                                                                                                                                                                                                  |

| PPI                 | Configuration interface for PPI channels and groups reserved for an application.                                                                                                                                                                                                                                                                                           |

| Radio Timeslot API  | Schedule other radio protocol activity, or periods of radio inactivity. See section 9.2.                                                                                                                                                                                                                                                                                   |

| Radio Notification  | Configure Radio Notification signals on ACTIVE and/or nACTIVE. See section 11.1.                                                                                                                                                                                                                                                                                           |

| Block Encrypt (ECB) | Safe use of 128-bit AES encrypt HW accelerator.                                                                                                                                                                                                                                                                                                                            |

| Event API           | Fetch asynchronous events generated by the SoC Library.                                                                                                                                                                                                                                                                                                                    |

| Flash memory API    | Application access to flash write, erase, and protect. Can be safely used during all protocol stack states. See section 8.                                                                                                                                                                                                                                                 |

| Temperature         | Application access to the temperature sensor.                                                                                                                                                                                                                                                                                                                              |

D00001681

# 7 System on Chip resource requirements

This section describes how the SoftDevice, including the Master Boot Record (MBR), uses the System on Chip (SoC) resources. The SoftDevice requirements are shown for both when the SoftDevice is enabled and disabled.

The SoftDevice and MBR (section 12) are designed to be installed on the nRF SoC in the lower part of the code memory space. After a reset, the MBR will use some RAM to store state information. When the SoftDevice is enabled, it uses resources on the SoC including RAM and hardware peripherals like the radio. For the amount of RAM required by the SoftDevice see section 14.

# 7.1 Hardware peripherals

Hardware access types are used to indicate the availability of hardware peripherals to the application. The availability varies per hardware peripheral and depends on whether the SoftDevice is enabled or disabled.

| Access type | Description                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|

| Restricted  | Used by the SoftDevice and outside the application sandbox.<br>The application has limited access through the SoftDevice API. |

| Blocked     | Used by the SoftDevice and outside the application sandbox.<br>The application has no access.                                 |

| Open        | Not used by the SoftDevice.<br>The application has full access.                                                               |

### Table 7-1. Hardware access type definitions

#### Table 7-2. Peripheral protection and usage by SoftDevice

| ID | Base address | Instance                                         | Access               | Access              |

|----|--------------|--------------------------------------------------|----------------------|---------------------|

|    |              |                                                  | SoftDevice enabled   | SoftDevice disabled |

| 0  | 0x40000000   | CLOCK                                            | Restricted           | Open                |

| 0  | 0x40000000   | POWER                                            | Restricted           | Open                |

| 0  | 0x40000000   | BPROT                                            | Restricted           | Open                |

| 1  | 0x40001000   | RADIO                                            | Blocked <sup>2</sup> | Open                |

| 2  | 0x40002000   | UARTO / UARTEO                                   | Open                 | Open                |

| 3  | 0x40003000   | TWIMO / TWISO /<br>SPIMO / SPISO / SPIO<br>/TWIO | Open                 | Open                |

<sup>2</sup> Available to the application through the Radio Timeslot API, see section 9.2.

| ID | Base address | Instance                                          | Access               | Access              |

|----|--------------|---------------------------------------------------|----------------------|---------------------|

|    |              |                                                   | SoftDevice enabled   | SoftDevice disabled |

| 4  | 0x40004000   | SPI1 / TWIS1 /<br>SPIM1 / TWI1 /<br>TWIM1 / SPIS1 | Open                 | Open                |

|    |              |                                                   |                      |                     |

| 6  | 0x40006000   | GPIOTE                                            | Open                 | Open                |

| 7  | 0x40007000   | SAADC                                             | Open                 | Open                |

| 8  | 0x40008000   | TIMER0                                            | Blocked <sup>3</sup> | Open                |

| 9  | 0x40009000   | TIMER1                                            | Open                 | Open                |

| 10 | 0x4000A000   | TIMER2                                            | Open                 | Open                |

| 11 | 0x4000B000   | RTC0                                              | Blocked              | Open                |

| 12 | 0x4000C000   | ТЕМР                                              | Restricted           | Open                |

| 13 | 0x4000D000   | RNG                                               | Restricted           | Open                |

| 14 | 0x4000E000   | ECB                                               | Restricted           | Open                |

| 15 | 0x4000F000   | ССМ                                               | Blocked <sup>4</sup> | Open                |

| 15 | 0x4000F000   | AAR                                               | Blocked⁵             | Open                |

| 16 | 0x40010000   | WDT                                               | Open                 | Open                |

| 17 | 0x40011000   | RTC1                                              | Open                 | Open                |

| 18 | 0x40012000   | QDEC                                              | Open                 | Open                |

| 19 | 0x40013000   | LPCOMP / COMP                                     | Open                 | Open                |

| 20 | 0x40014000   | EGU0 / SWI0                                       | Open                 | Open                |

3 Available to the application through the Radio Timeslot API, see section 9.2.

4 Available to the application through the Radio Timeslot API, see section 9.2.

5 Available to the application through the Radio Timeslot API, see section 9.2.

| ID | Base address | Instance                             | Access                  | Access              |

|----|--------------|--------------------------------------|-------------------------|---------------------|

|    |              |                                      | SoftDevice enabled      | SoftDevice disabled |

| 21 | 0x40015000   | EGU1 / SWI1 /<br>Radio Notifications | Restricted <sup>6</sup> | Open                |

| 22 | 0x40016000   | EGU2 / SWI2 /<br>SoftDevice Event    | Blocked                 | Open                |

| 23 | 0x40017000   | EGU3 / SWI3                          | Open                    | Open                |

| 24 | 0x40018000   | EGU4 / SWI4                          | Blocked                 | Open                |

| 25 | 0x40019000   | EGU5 / SWI5                          | Blocked                 | Open                |

|    |              |                                      |                         |                     |

| 30 | 0x4001E000   | NVMC                                 | Restricted              | Open                |

| 31 | 0x4001F000   | PPI                                  | Open <sup>7</sup>       | Open                |

| 32 | 0x40020000   | MWU                                  | Restricted <sup>8</sup> | Open                |

| 33 | 0x40021000   | PWM1                                 | Open                    | Open                |

| 34 | 0x40022000   | PWM2                                 | Open                    | Open                |

| 35 | 0x40023000   | SPI2 / SPIS2 / SPIM2                 | Open                    | Open                |

| 36 | 0x40024000   | RTC2                                 | Open                    | Open                |

| 37 | 0x40025000   | 125                                  | Open                    | Open                |

| 38 | 0x40026000   | FPU                                  | Open                    | Open                |

| NA | 0x10000000   | FICR                                 | Blocked                 | Blocked             |

| NA | 0x10001000   | UICR                                 | Restricted              | Open                |

| NA | 0x5000000    | GPIO PO                              | Open                    | Open                |

6 Blocked only when Radio Notification signal is enabled. See section 7.2 for software interrupt allocation.

7 See section 7.3 for limitations on the use of PPI when the SoftDevice is enabled.

8 See section 5.4 and section 7.5 for limitations on the use of MWU when the SoftDevice is enabled.

| ID | Base address | Instance | Access                  | Access              |

|----|--------------|----------|-------------------------|---------------------|

|    |              |          | SoftDevice enabled      | SoftDevice disabled |

| NA | 0xE000E100   | NVIC     | Restricted <sup>9</sup> | Open                |

# 7.2 Application signals – Software Interrupts (SWI)

Software Interrupts are used by the SoftDevice to signal events to the application.

#### Table 7-3. Allocation of Software Interrupt vectors to SoftDevice signals

| SWI | Peripheral ID | SoftDevice Signal                                          |

|-----|---------------|------------------------------------------------------------|

| 0   | 20            | Unused by the SoftDevice and available to the application. |

| 1   | 21            | Radio Notification – optionally<br>configured through API. |

| 2   | 22            | SoftDevice Event Notification.                             |

| 3   | 23            | Reserved.                                                  |

| 4   | 24            | SoftDevice processing - not user configurable.             |

| 5   | 25            | SoftDevice processing - not user configurable.             |

<sup>9</sup> Not protected. For robust system function, the application program must comply with the restriction and use the NVIC API for configuration when the SoftDevice is enabled.

# 7.3 Programmable Peripheral Interconnect (PPI)

The Programmable Peripheral Interconnect may be configured using the PPI API in the SoC Library.

This API is available both when the SoftDevice is disabled and when it is enabled. It is also possible to configure the PPI using the Cortex Microcontroller Software Interface Standard (CMSIS) directly when the SoftDevice is disabled.

When the SoftDevice is disabled, all PPI channels and groups are available to the application. When the SoftDevice is enabled, some PPI channels and groups, as described in the table below, are in use by the SoftDevice.

When the SoftDevice is enabled, the application program shall not change the configuration of PPI channels or groups used by the SoftDevice. Failing to comply with this will cause the SoftDevice to not operate properly.

#### Table 7-4. Assigning PPI channels between the application and SoftDevice

| PPI channel allocation | SoftDevice enabled             | SoftDevice disabled |

|------------------------|--------------------------------|---------------------|

| Application            | Channels 0 – 16                | Channels 0 – 19     |

| SoftDevice             | Channels 17 – 19 <sup>10</sup> | -                   |

#### Table 7-5. Assigning preprogrammed channels between the application and SoftDevice

| PPI channel allocation | SoftDevice enabled | SoftDevice disabled |

|------------------------|--------------------|---------------------|

| Application            | -                  | Channels 20 – 31    |

| SoftDevice             | Channels 20 – 31   | -                   |

#### Table 7-6. Assigning PPI groups between the application and SoftDevice

| PPI channel allocation | SoftDevice enabled | SoftDevice disabled |

|------------------------|--------------------|---------------------|

| Application            | Channels 0 – 3     | Channels 0 – 5      |

| SoftDevice             | Channels 4 – 5     | -                   |

<sup>&</sup>lt;sup>10</sup> Available to the application in Radio Timeslot API timeslots (section 9.2)

# 7.4 SVC number ranges

Application programs and SoftDevices use certain SVC numbers.

The table below shows which SVC numbers an application program can use and which numbers are used by the SoftDevice.

Important: The SVC number allocation does not change with the state of the SoftDevice (enabled or disabled).

#### Table 7-7. SVC number allocation

| PPI channel allocation | SoftDevice enabled | SoftDevice disabled |

|------------------------|--------------------|---------------------|

| Application            | 0x00-0x0F          | 0x00-0x0F           |

| SoftDevice             | 0x10-0xFF          | 0x10-0xFF           |

# 7.5 Peripheral runtime protection

To prevent the application from accidentally disrupting the protocol stack in any way, the application sandbox also protects the peripherals used by the SoftDevice.

Protected peripheral registers are readable by the application. An attempt to perform a write to a protected peripheral register will result in a Hard Fault. See section 4.2 for more details on faults due to prohibited memory access. Note that the peripherals are only protected when the SoftDevice is enabled; otherwise they are available to the application. See Table 7-2 for an overview of the peripherals with access restrictions due to the SoftDevice.

# 7.6 External and miscellaneous requirements

For correct operation of the SoftDevice, it is a requirement that the 16MHz crystal oscillator (16MHz XOSC) startup time is less than 1.5ms.

The external clock crystal and other related components must be chosen accordingly. Data for the crystal oscillator input can be found in the product specification for the SoC (nRF52832 Product Specification).

When the SoftDevice is enabled the SEVONPEND flag in the SCR register of the CPU shall only be changed from main or low interrupt level (priority not higher than 4), otherwise the behaviour of the SoftDevice is undefined and the SoftDevice might malfunction.

# 8 Flash memory API

The System on Chip (SoC) Flash Memory API provides the application with flash write, flash erase, and flash protect support through the SoftDevice. Asynchronous flash memory operations can be safely performed during active ANT communication using the Flash Memory API of the SoC Library.

The flash memory accesses are scheduled to not disturb radio events. See section 15.2 for details. If the protocol radio events are in a critical state, flash memory accesses may be delayed for a long period resulting in a timeout event. In this case, NRF\_EVT\_FLASH\_OPERATION\_ERROR will be returned in the application event handler. If this happens, retry the flash memory operation.

**Important:** Flash page (4096 bytes) erase can take up to 90ms and a 4 byte flash write can take up to 338µs. A flash write must be made in chunks smaller than or equal to the flash page size. Make flash writes in the smallest chunks possible to increase the probability of success, and reduce the chances of affecting ANT performance.

# 8.1 Using flash with ANT activity

The SoC Library API can safely be used during ANT radio activities to perform asynchronous flash memory operations.

The flash memory access is scheduled between the protocol radio events. For certain memory access operations, the time required may be longer than the time between radio events. In this case, the radio event may be skipped or the flash memory access may be delayed. If the flash operation requires more time than allowed to run concurrently with certain ANT activities, the flash memory access may fail and generate a timeout event: NRF\_EVT\_FLASH\_OPERATION\_ERROR. In this case, retry the flash operation.

| ANT Activity                                                                                                                                               | Flash Write                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANT Rx Scanning Channel<br>ANT Rx Search/Background Search<br>ANT Rx High Duty Search<br>ANT Tx/Rx Broadcast Messaging<br>ANT Tx/Rx Acknowledged Messaging | <ul> <li>Supports full flash write size (256 words).</li> <li>Flash timeout event may be generated if critical ANT radio activities need to occur.</li> <li>ANT transmit/receive performance may be impacted if continuous flash write operations are requested.</li> </ul> |

| ANT Tx/Rx Burst Transfer                                                                                                                                   | <ul> <li>Maximum recommended flash write size is 64 words. Larger flash writes may result in flash timeout events or burst transfer failures.</li> <li>Continuous flash write activity may result in burst transfers taking up to 2-3 times longer to complete.</li> </ul>  |

| ANT Activity                                                                                                                                               | Flash Erase                                                                                                                                                                                                                                                                 |

| ANT Rx Scanning Channel<br>ANT Rx Search<br>ANT Tx/Rx Broadcast Messaging<br>ANT Tx/Rx Acknowledged Messaging                                              | <ul> <li>Supports flash erase attempts.</li> <li>Flash timeout event may be generated if critical ANT radio activities need to occur.</li> <li>ANT transmit/receive performance may be impacted if continuous flash erase operations are requested.</li> </ul>              |

| ANT Tx/Rx Burst Transfer<br>ANT Rx High Duty Search                                                                                                        | • Flash erase not supported. Flash erase attempts may result in flash timeout event or burst transfer failures.                                                                                                                                                             |

# Table 8-1. Behaviour with ANT traffic and concurrent flash write/erase

# 9 Multiprotocol support

Multiprotocol support allows a developer to implement a custom 2.4 GHz proprietary protocol in the application; both while the SoftDevice is not in use (non-concurrent), and while the SoftDevice protocol stack is in use (concurrent). For concurrent multiprotocol implementations, the Radio Timeslot API allows the application protocol to safely schedule radio usage between ANT events.

# 9.1 Non-concurrent multiprotocol implementation

For non-concurrent operation a proprietary 2.4 GHz protocol can be implemented in the application program area and can access all hardware resources when the SoftDevice is disabled. The SoftDevice may be disabled and enabled without resetting the application in order to switch between a proprietary protocol stack and ANT communication.

# 9.2 Concurrent multiprotocol implementation using the Radio Timeslot API

The Radio Timeslot API allows the nRF52 device to be part of a network using the SoftDevice protocol stack and an alternative network of wireless devices using a custom protocol at the same time.

The Radio Timeslot (or, simply, Timeslot) feature gives the application access to the radio and other restricted peripherals during defined time intervals, denoted as timeslots. The Timeslot feature achieves this by cooperatively scheduling the application's use of these peripherals with those of the SoftDevice. Using this feature, the application can run other radio protocols (third party custom or proprietary protocols running from application space) concurrently with the internal protocol stack of the SoftDevice. It can also be used to suppress SoftDevice radio activity and to reserve guaranteed time for application activities with hard timing requirements, which cannot be met by using the SoC Radio Notifications.

The Timeslot feature is part of the SoC Library. The feature works by having the SoftDevice time-multiplex access to peripherals between the application and itself. Through the SoC Library API, the application can open a Timeslot session and request timeslots. When a Timeslot request is granted, the application has exclusive and real-time access to the normally blocked RADIO, TIMERO, CCM, and AAR peripherals and can use these freely for the duration (length) of the timeslot, see Table 7-1 and Table 7-2.

# 9.2.1 Request types

There are two types of Radio Timeslot requests, *earliest possible* Timeslot requests and *normal* Timeslot requests.

Timeslots may be requested as *earliest possible*, in which case the timeslot occurs at the first available opportunity. In the request, the application can limit how far into the future the timeslot may be placed.

**Important:** The first request in a session must always be earliest possible to create the timing reference point for later timeslots.

Timeslots may also be requested at a given time (*normal*). In this case, the application specifies in the request when the timeslot should start and the time is measured from the start of the previous timeslot.

The application may also request an extension to an ongoing timeslot. Extension requests may be repeated, prolonging the timeslot even further.

Timeslots requested as *earliest possible* are useful for single timeslots and for non-periodic or non-timed activity. Timeslots requested at a given time relative to the previous timeslot are useful for periodic and timed activities; for example, a periodic proprietary radio protocol. Timeslot extension may be used to secure as much continuous radio time as possible for the application; for example, running an 'always on' radio listener.

# 9.2.2 Request priorities

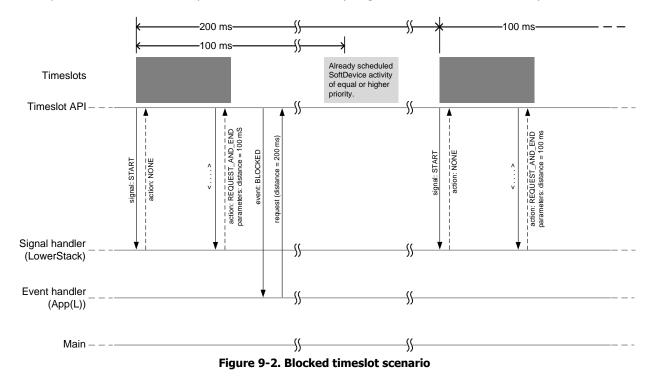

Radio Timeslots can be requested at either high or normal priority, indicating how important it is for the application to access the specified peripherals. A Timeslot request can only be blocked or cancelled due to an overlapping SoftDevice activity that has a higher scheduling priority.

# 9.2.3 Timeslot length

A Radio Timeslot is requested for a given length of time. Ongoing timeslots have the possibility to be extended.

The length of the timeslot is specified by the application in the Timeslot request and ranges from 100µs to 100ms. A timeslot may be extended multiple times, as long as its duration does not extend beyond the time limits set by other SoftDevice activities, and up to a maximum length of 128s.

# 9.2.4 Scheduling

The SoftDevice includes a scheduler which manages radio timeslots, priorities and sets up timers to grant timeslots.

Whether a Timeslot request is granted and access to the peripherals is given is determined by the following factors:

- The time the request is made,

- The exact time in the future the timeslot is requested for,

- The desired priority level of the request,

- The length of the requested timeslot.

Section 15.3 explains how timeslots are scheduled. Timeslots requested at high priority will cancel other activities scheduled at lower priorities in case of a collision. Requests for short timeslots have a higher probability of succeeding than requests for longer timeslots because shorter timeslots are easier to fit into the schedule.

**Important:** Radio Notification signals behave the same way for timeslots requested through the Radio Timeslot interface as for SoftDevice internal activities. See section 11.1 for more information. If Radio Notifications are enabled, Radio Timeslots will be notified.

# 9.2.5 Performance considerations

The Radio Timeslot API shares core peripherals with the SoftDevice, and application-requested timeslots are scheduled along with other SoftDevice activities. Therefore, the use of the Timeslot feature may influence the performance of the SoftDevice.

The configuration of the SoftDevice should be considered when using the Radio Timeslot API. A configuration which uses more radio time for native protocol operation will reduce the available time for serving timeslots and result in a higher risk of scheduling conflicts.

All Timeslot requests should use the lowest priority to minimize disturbances to other activities. At this priority level only flash writes might be affected. The high priority should only be used when required, such as for running a radio protocol with certain timing requirements that are not met by using normal priority. By using the highest priority available to the Timeslot API, non-critical SoftDevice radio protocol traffic may be affected. The SoftDevice radio protocol has access to higher priority levels than the application. These levels will be used for important radio activity, for instance when the device is about to lose a connection.

See section 9.2.4 for more information on how priorities work together with other modules e.g. the ANT protocol stack, the Flash API etc.

Timeslots should be kept as short as possible in order to minimize the impact on the overall performance of the device. Requesting a short timeslot will make it easier for the scheduler to fit in between other scheduled activities. The timeslot may later be extended. This will not affect other sessions as it is only possible to extend a timeslot if the extended time is unreserved.

It is important to ensure that a timeslot has completed its outstanding operations before the time it is scheduled to end (based on its starting time and requested length), otherwise the SoftDevice behaviour is undefined and may result in an unrecoverable fault.

# 9.2.6 Radio Timeslot API

This section describes the calls, events, signals, and return actions of the Radio Timeslot API.

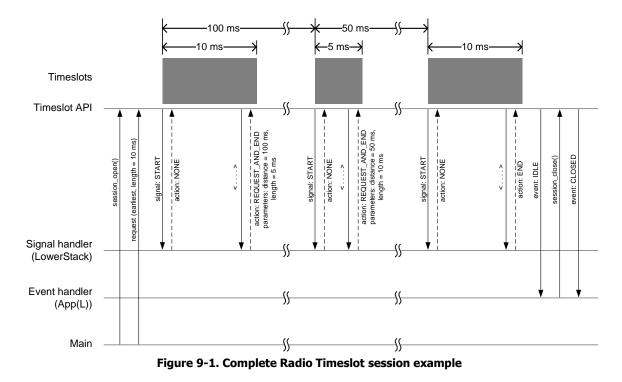

A Timeslot session is opened and closed using API calls. Within a session, there is an API call to request timeslots. For communication back to the application the feature will generate events, which are handled by the normal application event handler, and signals, which must be handled by a callback function (the signal handler) provided by the application. The signal handler can also return actions to the SoftDevice. Within a timeslot, only the signal handler is used.

**Important:** The API calls, events, and signals are only given by their full names in the tables where they are listed the first time. Elsewhere, only the last part of the name is used.

# 9.2.6.1 API calls

These are the API calls defined for the S212 SoftDevice:

#### Table 9-1. API calls

| API Call                            | Description                     |

|-------------------------------------|---------------------------------|

| <pre>sd_radio_session_open()</pre>  | Open a radio timeslot session.  |

| <pre>sd_radio_session_close()</pre> | Close a radio timeslot session. |

| <pre>sd_radio_request()</pre>       | Request a radio timeslot.       |

# 9.2.6.2 Radio Timeslot events

Events are generated by the SoftDevice scheduler and are used for Radio Timeslot session management.

Events are received in the application event handler callback function, which will typically be run in an application interrupt; see section 4.1. The following events are defined:

# Table 9-2. Radio Timeslot events

| Events                                       | Description                                                                                                                                   |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| NRF_EVT_RADIO_SESSION_IDLE                   | Session status: The current timeslot session has no remaining scheduled timeslots.                                                            |

| NRF_EVT_RADIO_SESSION_CLOSED                 | Session status: The timeslot session is closed and all acquired resources are released.                                                       |

| NRF_EVT_RADIO_BLOCKED                        | Timeslot status: The last requested timeslot could not be scheduled, due to a collision with already scheduled activity or for other reasons. |

| NRF_EVT_RADIO_CANCELLED                      | Timeslot status: The scheduled timeslot was cancelled due to an overlapping activity of higher priority.                                      |

| NRF_EVT_RADIO_SIGNAL_CALLBACK_INVALID_RETURN | Signal handler: The last signal hander return value contained invalid parameters and the timeslot was ended.                                  |

# 9.2.6.3 Radio Timeslot signals

Signals come from the peripherals and arrive within a Radio Timeslot.

Signals are received in a signal handler callback function that the application must provide. The signal handler runs in interrupt priority level 0, which is the highest priority in the system, see section 16.2.

| Table 9-3. Radio | <b>Timeslot signals</b> |

|------------------|-------------------------|

|------------------|-------------------------|

| Signal                                          | Description                                                                                                             |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| NRF_RADIO_CALLBACK_SIGNAL_TYPE_START            | Start of the timeslot. The application now has exclusive access to the peripherals for the full length of the timeslot. |

| NRF_RADIO_CALLBACK_SIGNAL_TYPE_RADIO            | Radio interrupt, for more information, see chapter 2.4 GHz radio (RADIO) in the nRF52 Reference Manual.                 |

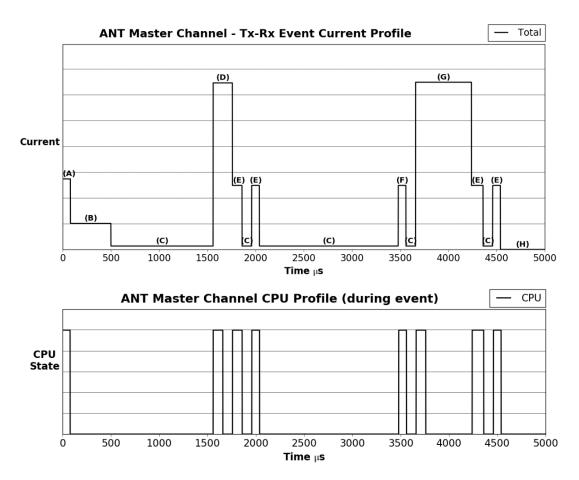

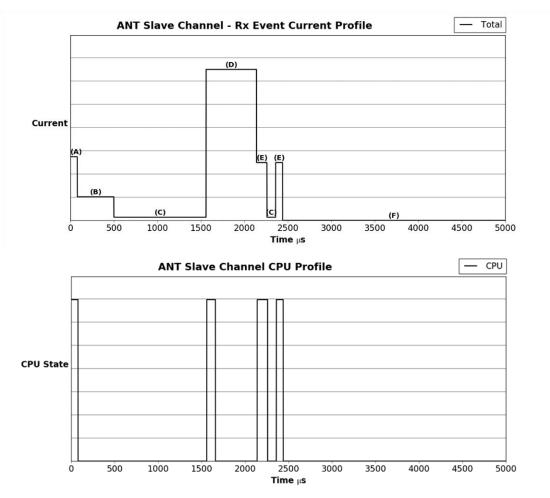

| NRF_RADIO_CALLBACK_SIGNAL_TYPE_TIMER0           | Timer interrupt, for more information, see chapter<br>Timer/counter (TIMER) in the nRF52 Reference Manual.              |